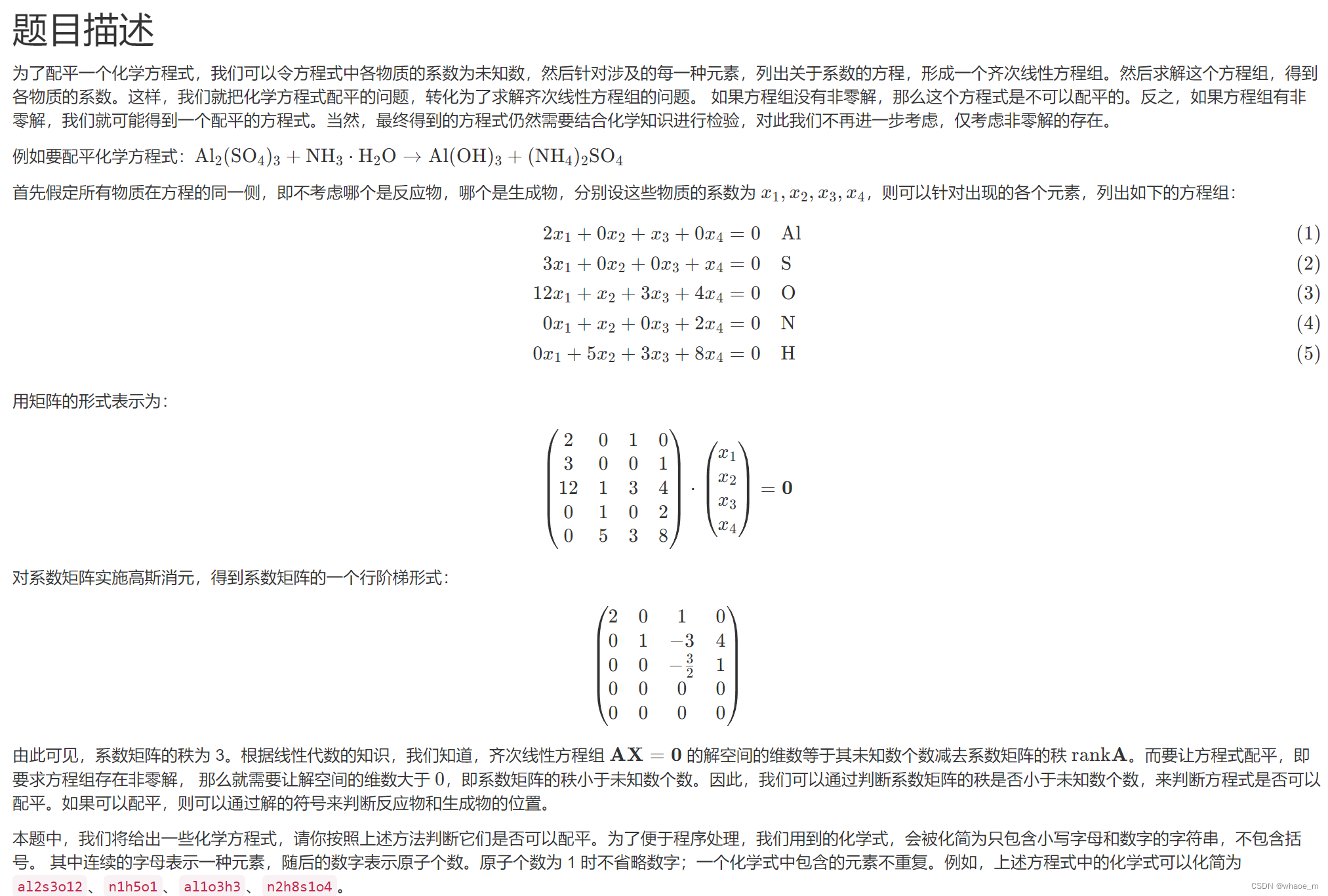

一、前言

在xilinx fpga的degug过程中,经常出现由于时钟不对而导致的观测波形失败,要想能够解决这些问题需要了解其debug的组成环境以及之间的数据流。本文主要介绍debug过程中需要的时钟及各时钟之间的关系。

二、debug相关时钟

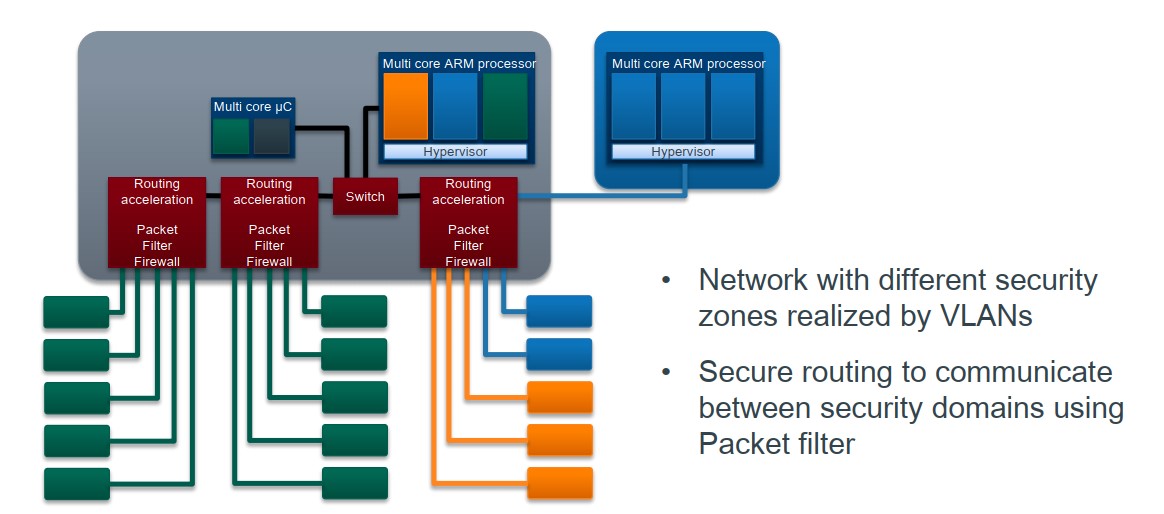

Vivado 硬件管理器使用 JTAG 接口与 Vivado Debug 内核进行通信,Debug Hub在 FPGA 器件的 JTAG 边界扫描 (BSCAN) 接口和 Vivado Debug 内核之间提供接口。因此,要想完成完整的数据流需要了解三个时钟,即JTAG时钟、Debug Hub时钟和Debug Core时钟。

2.1 JTAG时钟

该时钟同步JTAG边界扫描(BSCAN)接口的内部状态机操作。在连接到目标器件时,通常会在 Vivado 硬件管理器中选择 JTAG 时钟频率。

可以使用 Open New Hardware Target 向导(使用时需要先关闭hardware mannger)或以下 Tcl 命令来修改 JTAG 频率:

set_property PARAM.FREQUENCY 250000 [get_hw_targets*/xilinx_tcf/Digilent/210203327962A]

使用要求:如果设计包含调试内核,需要确保JTAG时钟比debug hub时钟慢2.5倍。

2.2 Debug Hub时钟

Vivado Debug Hub 内核,在 FPGA 器件的 JTAG 边界扫描 (BSCAN) 接口和 Vivado Debug 内核之间提供接口。如果 Vivado IDE 在设计实现(implementation)步骤中检测到调试内核,则会自动插入 Debug Hub 内核。Vivado IDE 在设计实现步骤中自动选择驱动 Debug Hub 内核的时钟。

Xilinx 推荐 debug hub时钟频率在 100MHz 左右或更低,因为 JTAG 时钟速度不需要特别高的频率。

如果需要改变debug hub时钟频率可以在设计编译后实现前通过TCL指令更改:

connect_debug_port dbg_hub/clk [get_nets <clock_net_name>]

也可以在设计编译后实现前通过TCL命令将debug hub的时钟缩减到100M(对于具有非常高速度时钟的设计,建议这样做):

set_property C_CLK_INPUT_FREQ_HZ 200000000 [get_debug_cores dbg_hub]

set_property C_ENABLE_CLK_DIVIDER true [get_debug_cores dbg_hub]

这两条命令允许在debug hub内核中包含基于MMCM的时钟分频器,以实现100 MHz的时钟频率。

2.3 Debug Core时钟

Vivado IP 目录中提供的所有调试内核都需要一个时钟,以确保与被监控的输入信号或由调试内核驱动的任何输出信号同步。在内核发现和调试测量阶段,需要时钟是自由运行和稳定的。此外,时钟还应与被监控或驱动的信号同步。否则可能会导致周期性的数据错误。

2.4 调试流程及时钟要求

Debug Hub IP 在主机(通过支持串行接口的 BSCAN Primitive)和芯片上的调试内核(通过支持并行接口的 XSDB 接口)之间架桥。BSCAN Primitive 时钟将数据串行移入和移出芯片到Debug Hub IP。Debug Hub IP 收集数据,并使用Debug Hub时钟将其发送到并行接口上的所有调试内核,反之亦然。如果任何调试内核时钟不能自由运行或不稳定,则最终会得到损坏的数据,从而导致vivado 输出"Debug Cores not detected"消息。为了避免任何数据损坏,在调试内核检测过程中,必须确保JTAG时钟和debug hub时钟稳定且自由运行。

- Debug Hub时钟必须是自由运行且稳定的。Xilinx 推荐时钟由适当约束且满足时序的时钟驱动器驱动。

- 如果时钟由MMCM/PLL驱动,则在进行任何调试内核测量之前,需要确保MMCM/PLL锁定信号为高电平。如果时钟连接到Debug Hub或任何调试内核,并且 MMCM/PLL LOCKED 信号在调试操作中间转换为 0,则时钟可能会出现明显的抖动,从而可能会导致调试逻辑出现不可预测行为。

- 需要让所有相关的时钟自由运行和稳定,才可以正常进行调试,获取数据。

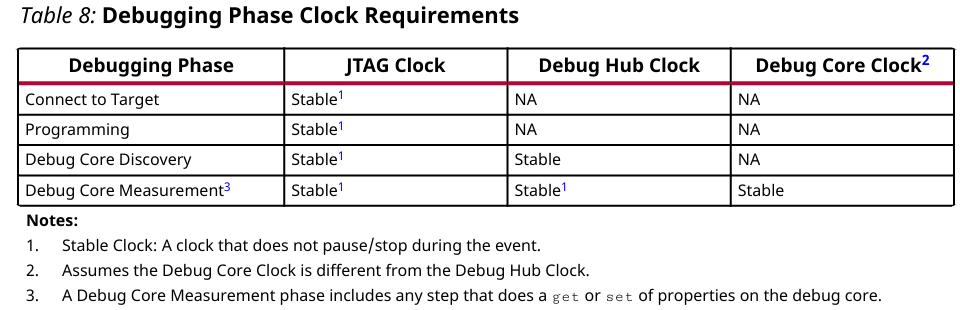

整个调试周期内各个时钟的要求如下表:

注:我自己在接手一个别人JESD204B建链不稳定的工程时,就发现 Vivado 时常会报ILA 时钟相关的错误,其原因就是该工程将JESD204B的恢复时钟作为了ILA核的时钟,而建链不稳定则恢复时钟也不稳,因此不满足上表中最后一行最后一列的 debug core clock应是稳定的要求,因此会导致vivado报错或者采不到波形。

三、相关报错

如果JTAG时钟处于非活动状态或不可用,将无法连接到硬件目标(hardware target)。

如果Debug Hub时钟处于非活动状态或不可用,Vivado硬件管理器会发出以下错误消息:

INFO: [Labtools 27-1434] Device xxx (JTAG device index = 0) is programmed

with a design that has no supported debug core(s) in it.WARNING: [Labtools 27-3123] The debug hub core was not detected at User Scan Chain 1

or 3.

Resolution:1. Make sure the clock connected to the debug hub (dbg_hub) core is a free

running clock and is active OR2. Manually launch hw_server with -e "set xsdb-user-bscan

<C_USER_SCAN_CHAIN scan_chain_number>" to detect the debug hub at User Scan Chain of 2 or 4. To determine the user scan chain setting, open the implemented design and use:

get_property C_USER_SCAN_CHAIN [get_debug_cores dbg_hub].如果任何调试核心时钟处于非活动状态或不可用,Vivado 硬件管理器会发出以下错误消息:

INFO: [Labtools 27-2302] Device xxx (JTAG device index = 1) is programmed

with a design that has 1 ILA core(s).CRITICAL WARNING: [Labtools 27-1433] Device xxx (JTAG device index = 1) is

programmed with a design that has an unrecognizable debug core (slave type = 17) at

user chain = 1, index = 0.Resolution: 1) Ensure that the clock signal connected to the debug core and/or debug hub is clean and

free-running.2) Ensure that the clock connected to the debug core and/or debug hub meets all timing constraints.3) Ensure that the clock connected to debug core and/or debug hub is faster than the JTAG clock frequency.注:在实际过程中还会有其他debug相关报错,不过大概率都是时钟的问题,从报错提示和上面时钟的要求入手解决即可。

四、参考资料

ug908:Vivado Design Suite User Guide Programming and Debugging