前文讲解了高速收发器的QPLL及CPLL和差分时钟相关内容,如下图所示。本文就打开高速收发器通道的内部结构,进行简要讲解。

收发器的内部框图如下所示,上半部分是发送通道,下半部分是接收通道,均包含PCS和PMA两部分。其中PMA的功能为:串并转换和模拟部分。PCS的功能为:并行的数字电路处理。

本文先讲解发送通道,接收通道的很多内容相似,只有部分区别,下图是发送通道的内部框图,搞懂这张图,基本上发送通道的功能就了解的差不多了。

1. FPGA TX Interface

GTX发送通道的用户接口,用户数据通过该接口的信号输入。用户输入的数据TXDATA与用户发送时钟TXUSRCLK2上升沿对齐,数据位宽可以设置为2、4、8字节,常用数据位宽4字节,即32位。

2、8B/10B Encoder

对待发送的数据进行8B/10B编码,作用与前文DVI接口的TMDS编码一致,直流均衡,保证已传输的数据中1和0的个数长期相等。

在配置IP时,可以选择发送/接收数据的编码/解码方式,如果把用户数据位宽设为32位,采用8B/10B编码,则编码后的数据位宽为40位,如下图所示。

这个数据的位宽大小其实与线速率和编码方式均有关,如下表所示,当使能8B/10B编码时,发送数据位宽TX_DATA_WIDTH只能设置为20、40、80。

注意表中TX_DATA_WIDTH表示一个用户数据经过8B10B编码后的数据位宽,而FPGA Interface Width表示用户接口每次传输的数据位宽,该数据与后文的TXUSRCLK2对齐。Internal Data Width表示PCS内部并行数据一个时钟传输的数据位宽,该数据与后文的TXUSRCLK对齐。

当TX_DATA_WIDTH与Internal Data Width相等时,表示PCS内部传输一个数据只需要一个时钟,此时TXUSRCLK的频率与TXUSRCLK2频率会相等。如果TX_DATA_WIDTH是Internal Data Width的二倍,则PCS内部需要两个时钟才能传输一个经过8B10B编码后的用户数据,那么TXUSRCLK的频率是TXUSRCLK2频率的2倍。可以在后文图12的时钟关系中进行验证。

PCS内部每次可以传输2字节或者4字节数据,通过TX_IN_DATAWIDTH参数进行设置,TX_IN_DATAWIDTH为0时每次传输2字节数据,为1时每次传输4字节数据,当线速率大于6.6Gb/S时,每次必须传输4字节数据。

因此由下表可知,当线速率为10Gb/S,使能8B/10B时,用户数据位宽只能为32或者64位,并且编码后的数据位宽均为40位。

当不使能8B/10B编码且线速率小于6.6Gb/S时,用户输入的数据位宽可以是16、20、32、40、64、80。此时如果TXDATA为16/32/64,TX_DATA_WIDTH为20/40/80,TXCHARDISPMODE和TXCHARDISPVAL端口用于将TXDATA端口从16位扩展到20位、32位扩展到40位或64位扩展到80位。如下图所示。

通过下图可知GTX先发送低字节数据,后发送高字节数据。

在多数情况下都是要使用8B/10B编码或者64B/66B编码的,此时TXCHARDISPMODE和TXCHARDISPVAL可以用来控制极性,与TMDS编码类似,直流均衡,硬核模块可以自己实现,用户也可以通过这两个信号自己实现。

采用8B/10B编码,每传输10bit数据,需要传输2bit无效数据。数据传输效率只有百分之八十,为了提高数据传输速率,同时保留编码方案的优势,可以使用64B/66B编码。

3. TX Gearbox

支持使用64B/66B编码,由图3可知,8B/10B Encoder和TX Gearbox的输入、输出都是连接的同一个端口。

因此在实际使用时,如果不使用编码,数据直接到达数据选择器输入端,然后输出。如果使用8B/10B编码,则会经过8B/10B Encoder到达数据选择器输入端。如果使用64B/66B则经TX Gearbox到达数据选择器输入端口。在使用64B66B编码时详细讲解该部分内容。

4. TX PIPE Control

全称为Physical Interface for PCI Express,PCIe物理层接口。如果使能PCIE接口,则该通道是PCIE的数据通道,否则将不会被使用。

5. Pattern Generator

伪随机序列(Pseudo-random bit sequences,PRBS),频谱接近白噪声,一般用于高速串行通信通道传输的误码率测试。相关的设置端口如下所示,原理与M序列类似。

手册中显示提供了四种PRBS波形,分别是PRBS-7、PRBS-15、PRBS-23、PRBS-31,其中PRBS-7的表达式为x^7+x^6+1,输出数据每2^7-1个时钟循环一次,实现方式也很简单,几个移位寄存器加异或门就行了。

6和16、TX Phase Interpolator Controller

TX相位插值器控制器模块,允许使用PCS中的TX相位插值器PPM(百万分之一)控制器模块来控制TX PMA中的TX PI,以优化高速数据传输过程中的信号质量,保持传输的稳定性和可靠性。

7. Phase Adjust FIFO

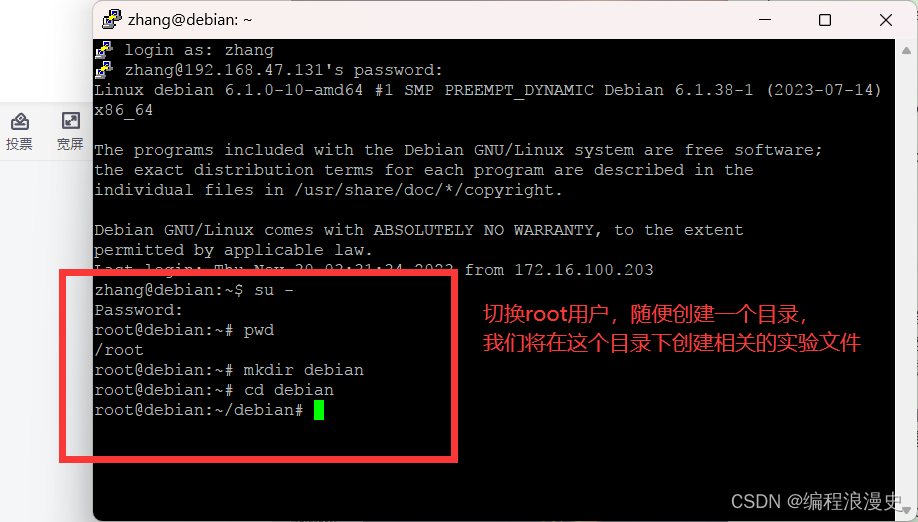

相位调整FIFO缓冲器如下图是时钟域的划分,在发送端的PCS子层里面有两个并行时钟域,分别是PMA相连的并行时钟(XCLK)和TXUSRCLK时钟。要传输数据,XCLK速率必须与TXUSRCLK速率匹配,并且必须解决两个域之间的所有相位差。

GTX的发送数据通道包括一个FIFO缓冲器和一个TX相位对准电路,用于解决XCLK和TXUSRCLK域之间的相位差。

FIFO缓冲器优势就是设计比较简单,用户可以不用去管内部实现,只需要在调用IP时勾选下图中1处选项即可,缺点是FIFO的延迟比较大,导致用户把数据输入GTX到GTX输出数据的时间比较长.如果不考虑这部分延迟,推荐直接使用FIFO即可。

如果对延时比较敏感,则可以使用相位对齐电路,只不过需要用户自己编写这部分控制代码,如果代码出现错误,将无法正常接收和发送数据。

在图10中还可以设置用户发送端口TXUSRCLK和用户接收端口RXUSRCLK的时钟来源,首先应该了解下TXUSRCLK和TXUSRCLK2。

TXUSRCLK是GTX发送通道中PCS逻辑的内部时钟,TXUSRCLK的速率取决于GTXE2_CHANNEL原语的内部数据路径宽度和GTX发送通道的线路速率,计算公式如下所示。

TXUSRCLK2是GTX发送通道所有信号的主同步时钟。TXUSRCLK2和TXUSRCLK的频率关系与TX_DATA_WIDTH、TX_INT_DATAWIDTH有关,如下图所示。

**TXUSRCLK和TXUSRCLK2必须正边沿对齐,并且源时钟必须相同,两者之间的偏斜尽可能小。**一般使用BUFG、BUFH、BUFR来驱动TXUSRCLK和TXUSRCLK2。

因此一般将GTX IP输出的TXOUTCLK时钟信号作为TXUSRCLK和TXUSRCL源时钟信号,用户其实只需要关注TXUSRCLK2和RXUSRCLK2即可,其余两个用于IP内部,与用户关系不大。

如果IP设置为图10所示,那么时钟关系如下所示,GTX IP输出的TXOUTCLK通过一个MMCM生成RXUSRCLK、RXUSRCLK2、TXUSRCLK、TXUSRCLK2时钟信号,全部输入GTX IP内部,其中RXUSRCLK2和TXUSRCLK2分别输出作为用户接收、发送的时钟信号。

图10的设置好处在于TXUSRCLK2和RXUSRCLK2信号是同一个信号,那么用户的发送端和接收端使用的是同一时钟信号,不需要跨时钟处理。

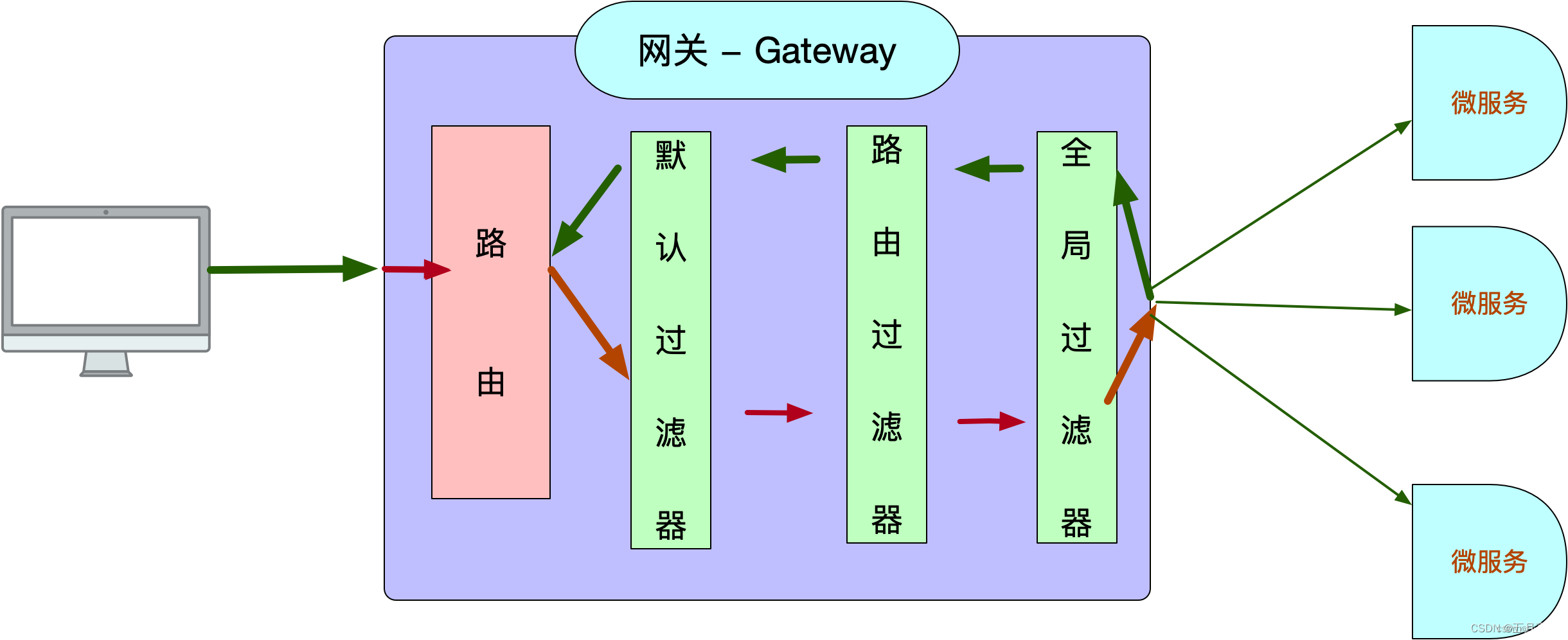

前文讲解了GTX的QPLL和CPLL等时钟信号,本文对外部时钟与发送、接收通道内部时钟的关联做简要介绍,下图是发送通道的时钟架构。

下图是发送通道内部的串行和并行时钟分频器,部分内容可以与前文的外部时钟相互对应。

下图是前文讲解QPLL和CPLL出现的图,上下两图中1处其实都是同一个器件,上图中IBUFGDS输出信号可以通过REFCLK_CTRL控制引脚输出到BUFG、BUFH、CMT,这是什么意思?

这就意味着GT bank的差分时钟转换为单端时钟后,可以作为其他bank的时钟信号,毕竟BUFG能够驱动FPGA内部所有时钟资源吧,不了解的可以查看前文对7系列FPGA时钟资源的讲解。但REFCLK_CTRL这个信号由软件自动生成,用户无法控制。

上图中的3处其实与下图的4处是相同结构,均是数据选择器、CPLL,上图4是QPLL的输出时钟和参考时钟,其中QPLL的输出时钟QPLLCLK和CPLL的输出时钟通过TXSYSCLKSEL[0]的选择作为TX PMA的输入时钟。

该时钟输入TX PMA之后,需要经过 “Phase Interp”后被D分频,然后分为两路,一路直接作为并串转换模块的串行时钟,另一类继续经过两次分频作为并串转换模块并行时钟,并且输出到PCS侧作为其时钟,还输入到下半部分的数据选择器中。

这里并串转换为什么会配置一个D分频的分频器?

首先要明确这个时钟的频率能够影响什么?作为并串转换的串行时钟,毫无疑问直接影响的就是转换后的数据的线速率,通过控制该分频器能够在一定范围内调节该通道的线速率。

这样就好回答具体原因了,每个GT bank有四个通道,但是却共用同一个QPLL,那如果四个通道的线速率均大于6.6Gb/S,但是线速率却不等,该如何实现?此时只能使用QPLL输出时钟,而QPLL输出时钟只有一个,此时就只能通过调节每个通道内部的D分频器,来实现不同通道不同线速率的目的。

但是D分频器只能实现1、2、4、8分频,分频系数可以动态设置也可以静态设置。当静态设置时,必须把分频系数TXOUT_DIV设置为固定值,并且将TXPATE设置为3’b000。

如果要实现动态线速率,需要在生成IP时勾选TXRATE信号,TXOUT_DIV和TXRATE必须在器件配置时选择相同的D分频器值,器件配置后,通过TXRATE动态更改D分频器值。

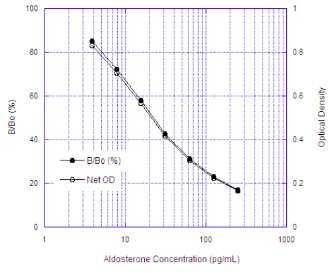

分频系数设置如下图所示,静态时通过TXOUT_DIV的值进行设置,动态时根据TXRATE的值进行设置,默认分频系数为1。

之后还要讲解下图14中后两个分频器的作用,这两个分频的输入作为并串转换模块的串行时钟,而输出作为并串转换模块的并行时钟,分频系数毫无疑问与并行数据位宽有关。

两个分频器能够组成的分频系数有8、10、16、20,由图5可知,PCS内部传输数据位宽只有16、20、32、40这几种,即并串转换的并行数据位宽取值为16、20、32、40。

可以推测串行数据是在串行时钟的双沿完成转换的,在8倍频率的时钟下将16位并行数据转换为串行数据输出,其他分频系数转换道理类似。

下图中的TXOUTCLKPCS和TXOUTCLKFABRIC用户不需要关注,没有输出到用户接口。

重点在于TXOUTCLK,时钟来源可以是TXOUTCLKPCS、TXOUTCLKPMA、QPLL或者CPLL参考时钟或参考时钟二分频,还可以选择是否对时钟来源进行延迟。

TXOUTCLK输出到BUFG,就处于“GTPE2_CHANNEL”外部了,根据用户的数据位宽,生成对应的参考时钟信号,下图是2字节或者4字节数据位宽时,可以使用的时钟结构。

用的比较多的应该是下图所示的时钟结构,TXOUTCLK输出到BUFG,然后通过MMCM生成TXUSCLK和TXUSCLK2,其中TXUSCLK2作为用户接口的时钟信号。图13就是使用的该结构生成用户时钟信号。

下图是单通道的TXOUTCLK通过MMCM生成TXUSRCLK和TXUSRCLK2驱动多个通道的时钟信号,这样做的好处应该是多个通道的数据都处于同一时钟域下,便于数据同步。

通过FIFO缓冲器引出了内部时钟的相关讲解,接下来回归正文,继续讲解下图中的其余资源, 将图在贴一遍,不然文章过长不好阅读。

8 .SATA OOB

SATA是硬盘接口,建立通信主要是通过检测OOB(Out Of Band)实现的,并且向上层传输连接情况,因此只有在使用SATA协议时,才会使用该模块,否则不用考虑。

9. PCIE Beacon

PICE唤醒功能,只有在使用PCIE协议时才会用到,否则不考虑。

10. Polarity

极性控制,这个作用比较大,主要时针对PCB设计时将差分对设计反了,模块内部可以将极性反转,从而解决PCB设计问题。

在生成IP时一般会勾选极性控制选项,后续如果PCB设计或者其他板卡引脚极性相反时,只需要将该信号设置为1’b1,将板卡内部的极性输出也翻转即可,如下图所示。

11. PISO

并串转换模块(parallel input Serial output),在前面讲解时钟分频时已经讲解过作用了,就是在时钟双沿将PCS发送的并行数据转换为串行数据。

12及14、 TX Pre/Post Emp和TX Driver

GTX的TX驱动器是高速电流模式差分输出缓冲器,如下图所示。为了最大限度地提高信号完整性,具有差分电压控制、光标前和光标后传输预加重、校准终端电阻功能。

需要明白一个道理,高速信号在长距离、线速率较高的传输时,损耗是很严重的。经过损耗衰减之后,为了让接收端还能检测到数据,在发送端会做预加重和去加重处理,增大差分输出信号的摆幅等等,让其经过传输损耗之后差分信号的幅值变为零。

用户只需要调节两个参数的值就可以调节预加重和去加重了,在配置IP时勾选下面两个选项即可。至于参数具体应该设置为多少,要根据实际的电路进行眼图扫描,然后确定最佳参数,关于眼图在接收通道的章节进行讲解。

13. TX OOB and PCIE

使用PCIE、SATA协议时才会使用的功能,否则不会用到。

15. TX Clock Dividers

这个就是时钟的分频模块,在前半段讲解的D分频及后续两个分频时已经详细讲解了,此处不再赘述。

终于写完GTX发送通道的相关内容了,手册这部分内容大概有接近70页,我只用了不到13页,部分暂时不会使用的内容暂时忽略,重点在于时钟的讲解,很多模块都是针对SATA、PCIE这些协议的,忽略这些,其实也还是比较简单的。

如果对文章内容理解有疑惑或者对代码不理解,可以在评论区或者后台留言,看到后均会回复!

如果本文对您有帮助,还请多多点赞👍、评论💬和收藏⭐!您的支持是我更新的最大动力!将持续更新工程!