Q:本篇我们在基本D触发器中添加一个复位控制信号来实现带异步复位功能的D触发器。

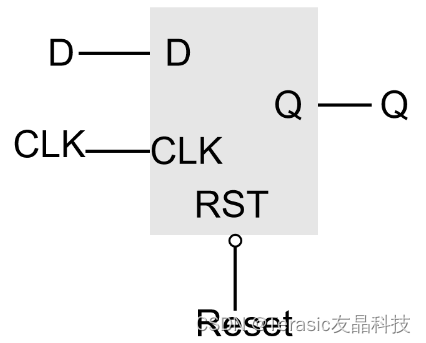

A:带复位控制信号(RST)的D触发器,当RST为0时,输出Q为0;当RST为1时,Q取决于D和CLK的输入。

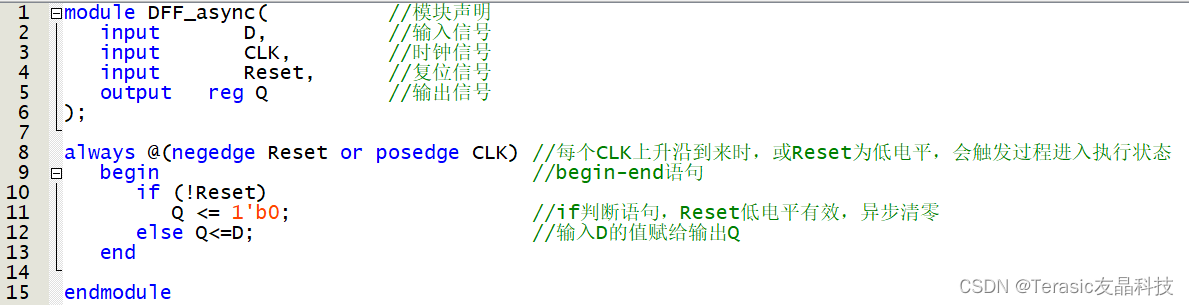

带复位信号控制信号的D触发器又有同步复位和异步复位之分。在时钟信号上升沿时完成复位,称之为同步复位;异步复位是指无论在时钟上升沿还是下降沿,都会执行清零复位操作。异步清零D触发器Verilog代码:

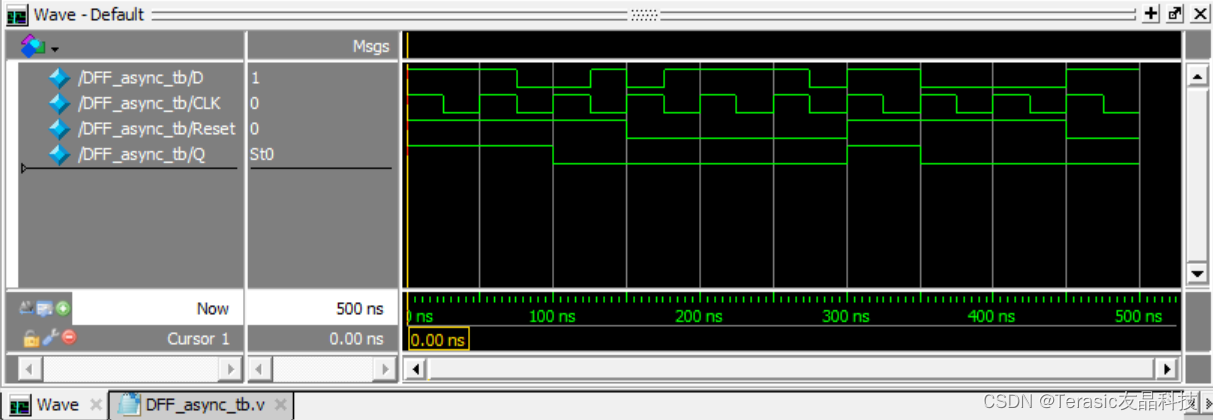

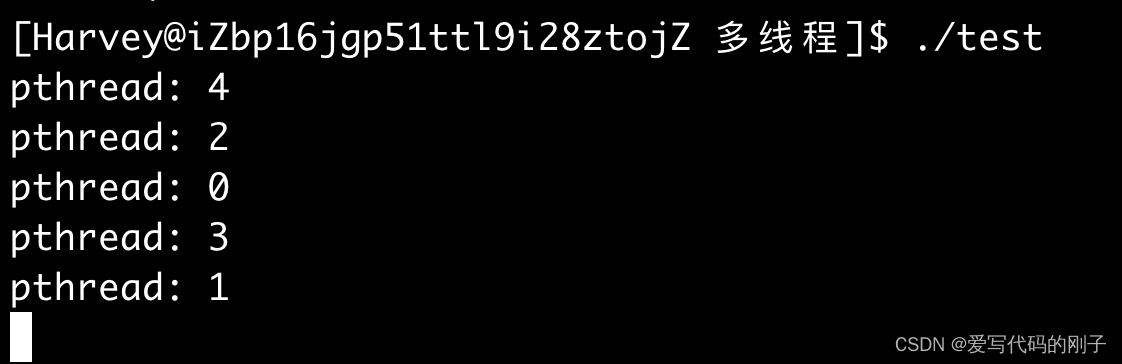

例化异步复位D触发器,使用DE2-115开发板的SW[0]作为数据输入D,KEY[0]作为时钟输入CLK,KEY[1]作为异步复位信号输入,LEDR0显示输出值Q。ModelSim仿真结果: