题目:

Verilog has a ternary conditional operator ( ? : ) much like C:

(condition ? if_true : if_false)

This can be used to choose one of two values based on condition (a mux!) on one line, without using an if-then inside a combinational always block.

解题:

module top_module (input [7:0] a, b, c, d,output [7:0] min);//// assign intermediate_result1 = compare? true: false;reg [7:0]zj1;reg [7:0]zj2;assign zj1 = (a<b)? a : b;assign zj2 = (c<d)? c : d;assign min = (zj1<zj2)? zj1 : zj2;endmodule

结果正确:

注意点:

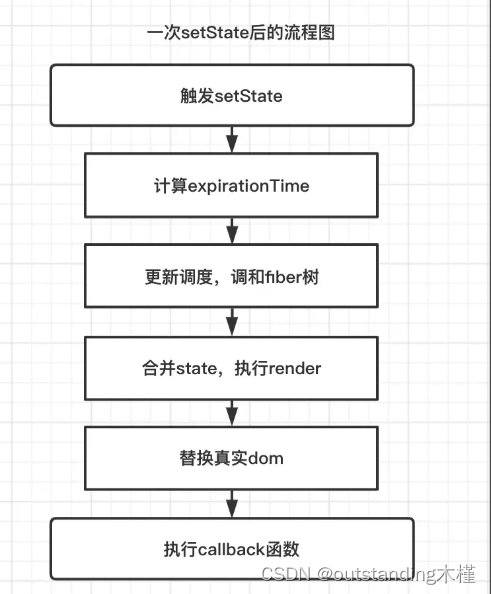

在 Verilog 中,三元条件运算符(Conditional Operator)通常用于根据条件选择不同的值。其一般形式如下:

result = (condition) ? value1 : value2;

其中,condition 是一个逻辑条件表达式,value1 和 value2 是根据条件判断所选择的两个值。如果 condition 为真,则结果 result 将被赋值为 value1;若 condition 为假,则结果 result 将被赋值为 value2。

![[算法学习]](https://img-blog.csdnimg.cn/direct/4cadc5f1197b43c4a5bea2b9fe57ee0a.png)