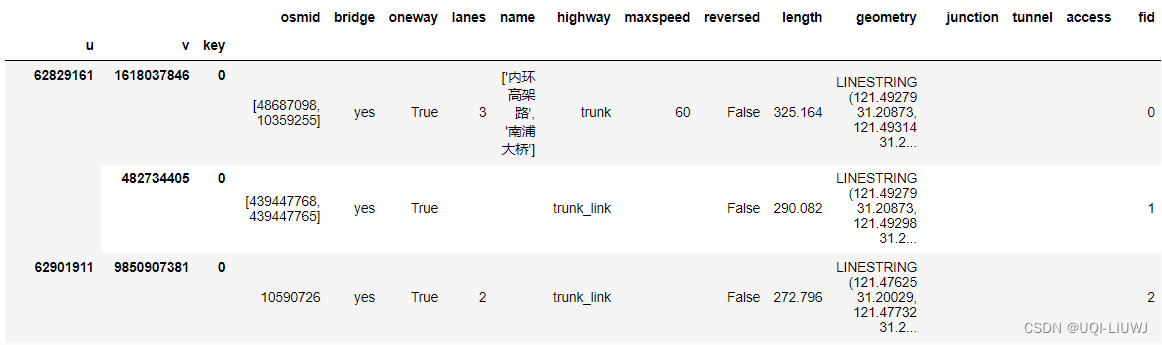

在可测性设计(DFT)技术中,scan的设计是其中非常重要的的一块内容,今天就来介绍一下业界常用的三种scan cell。

一般来说,一个scan cell有两个不同的可选择的输入。第一个输入为数据输入(data input),也就是电路的组合逻辑的输入端。而第二个输入是扫描输入(scan input),由上一个scan cell的输出驱动的,从而形成一个或多个移位寄存器链(shift registers),我们把它称为扫描链(scan chain)。这些扫描链可由外部直接访问,将扫描链中第一个scan cell的输入设为主输入(primary input),扫描链最后一个输出作为主输出(primary output)。

由于scan cell中有两个输入,因此要加入一个多路选择器使得scan cell在两种不同模式下工作:正常/捕获(capture)模式和移位(shift)模式。

在正常/capture模式下,选择数据输入来传送到输出。在移位模式下,选择扫描输入传送到输出。这样就可以把任意测试向量从一个或多个主输入灌入到所有扫描单元,同时通过一个或多个主输出移出所有扫描单元的测试向量数据。

在本文中,我们来介绍一下三种广泛使用的扫描单元设计:muxed-D scan、clock-scan和level-sensitive scan design(LSSD)设计。

1、Muxed-D Scan Cell

Muxed-D很容易理解了,结构示意图如下,边沿触发,它由D触发器和多路选择器组成。多路选择器使用扫描使能端(SE)来选择数据输入(DI)或扫描输入(SI)。

edge-triggered muxed-D scan cell

在正常/capture模式下,SE设置为0。当时钟时钟上升沿到来时,数据输入DI处的值被捕获到内部D触发器中。在shift模式下,SE设置为1。当D触发器的值被移出时,SI将新的数据移到D触发器。波形图如下:

优缺点:使用muxed-D扫描单元的主要优点是它们与使用单时钟D触发器的主流设计兼容,以及现有EDA提供的全面支持。缺点是每个muxed-D扫描单元在function path上增加了多路选择器导致的时钟延迟。

2、Clocked-Scan Cell

在scan的设计中,边缘触发的时钟扫描单元也可以用来代替D触发器,与muxed-D扫描单元类似,时钟扫描单元也有数据输入DI和扫描输入SI;而在时钟扫描单元中,使用两个独立的时钟进行输入选择,数据时钟DCK和shift时钟SCK。

clocked-scan cell

在正常/capture模式下,数据时钟DCK用来capture在数据输入DI到scan cell的值。在shift模式下,移位时钟SCK用于将新的数据从SI移到scan cell中去,当前scan cell的值将被移出。

优缺点:和muxed-D相比,主要优点是它不会导致数据输入的性能下降。主要的缺点是,它需要额外的移位时钟(SCK)线路。

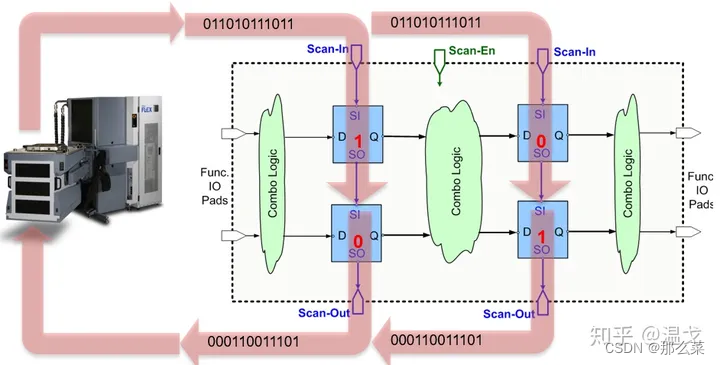

3、LSSD Scan Cell

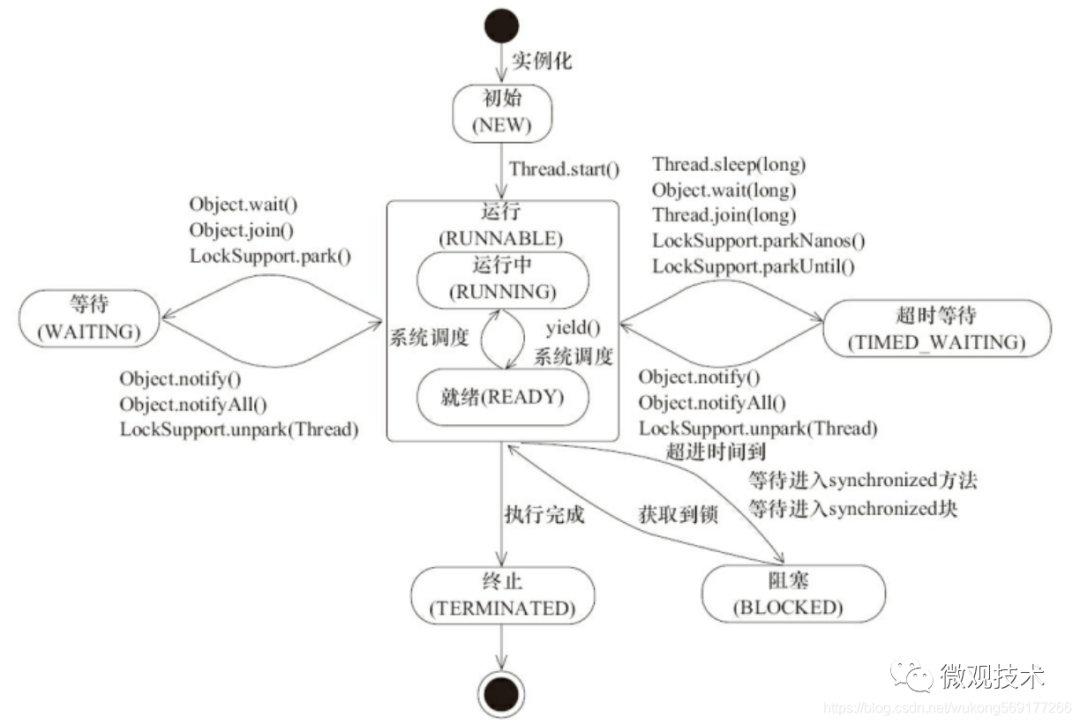

muxed-D scan cells 和 clocked-scan cells是基于flip-flop的边沿触发设计,LSSD是基于锁存器的电平敏感的设计。

如下图LSSD是由两个latch组成,A,B为shift clock,D为function clock. C为数据输入,I 为scan 输入。L1, L2为输出,都可以用来驱动组合逻辑。

LSSD示意图

LSSD原始电路图如下:

附带一个波形图以及真值表来帮助读者更好的理解其设计:

LSSD waveform

truth table

优缺点:LSSD scan cell的主要优点就是其可以应用到带有锁存器的设计中。缺点是需要引入额外的时钟,从而为布线增加了难度。

以上就是三种常用的scan cell的介绍,在实际的项目中,scan cell的设计都是通过EDA工具来完成的。