文章目录

- generate_for

- verilog code

- testbench code

- 仿真波形

- for 循环

- verilog code

- 仿真波形

- 错误小结

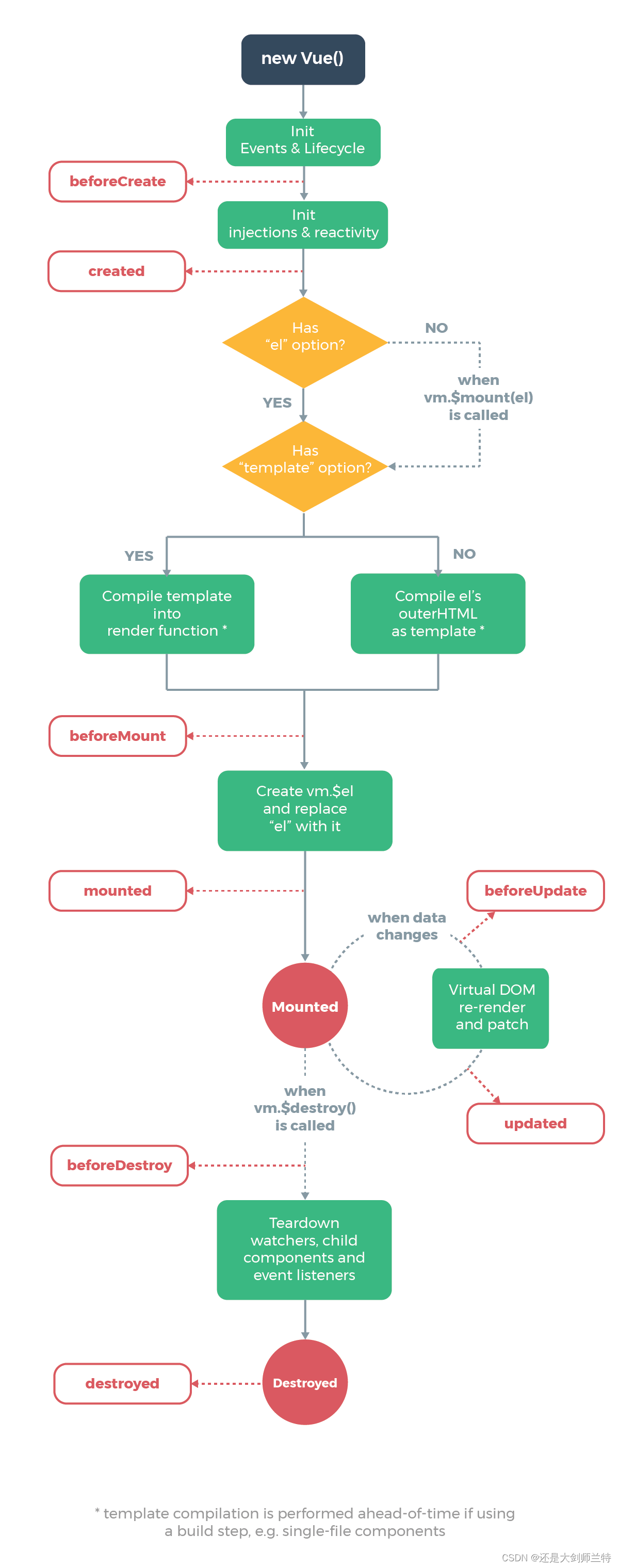

generate_for

在某个module中包含了很多相似的连续赋值语句,请使用generata…for语句编写代码,替代该语句,要求不能改变原module的功能。

使用Verilog HDL实现以上功能并编写testbench验证。

module template_module( input [7:0] data_in,output [7:0] data_out

);assign data_out [0] = data_in [7];assign data_out [1] = data_in [6];assign data_out [2] = data_in [5];assign data_out [3] = data_in [4];assign data_out [4] = data_in [3];assign data_out [5] = data_in [2];assign data_out [6] = data_in [1];assign data_out [7] = data_in [0];endmodule

输入描述:

data_in:8bit位宽的无符号数

输出描述:

data_out:8bit位宽的无符号数

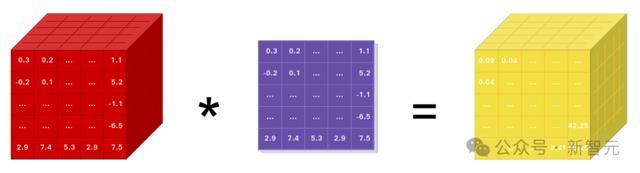

genrate for 和 C 代码中的 for 循环不一样,C 代码中的for 循环语句是串行执行的,generate for 的语句是并行执行的。

verilog code

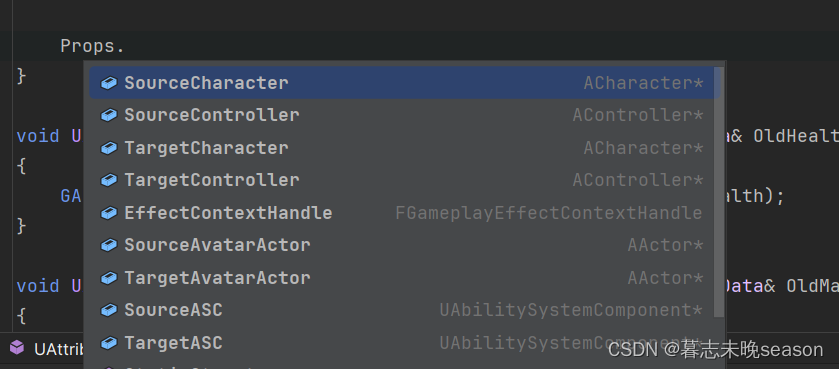

代码中注意以下几点:

- 不要使用非阻塞赋值

<=; - 不要忘了给 data_out 前面带 assign 关键字,因为 data_out 是 wire 类型;

- 一定要进行声明操作

genvar i,此外 for 语句中begin后面要有冒号: name

testbench code

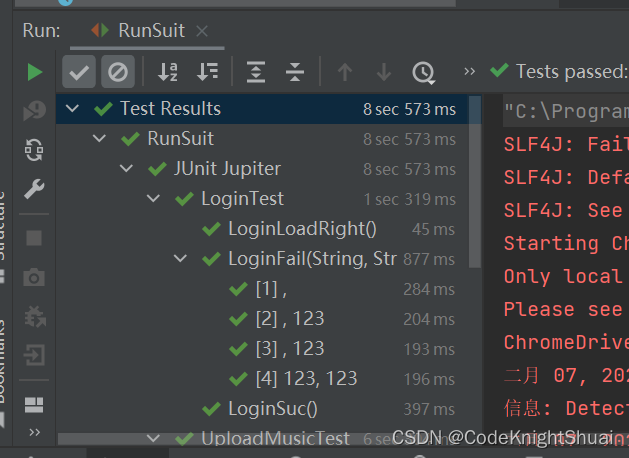

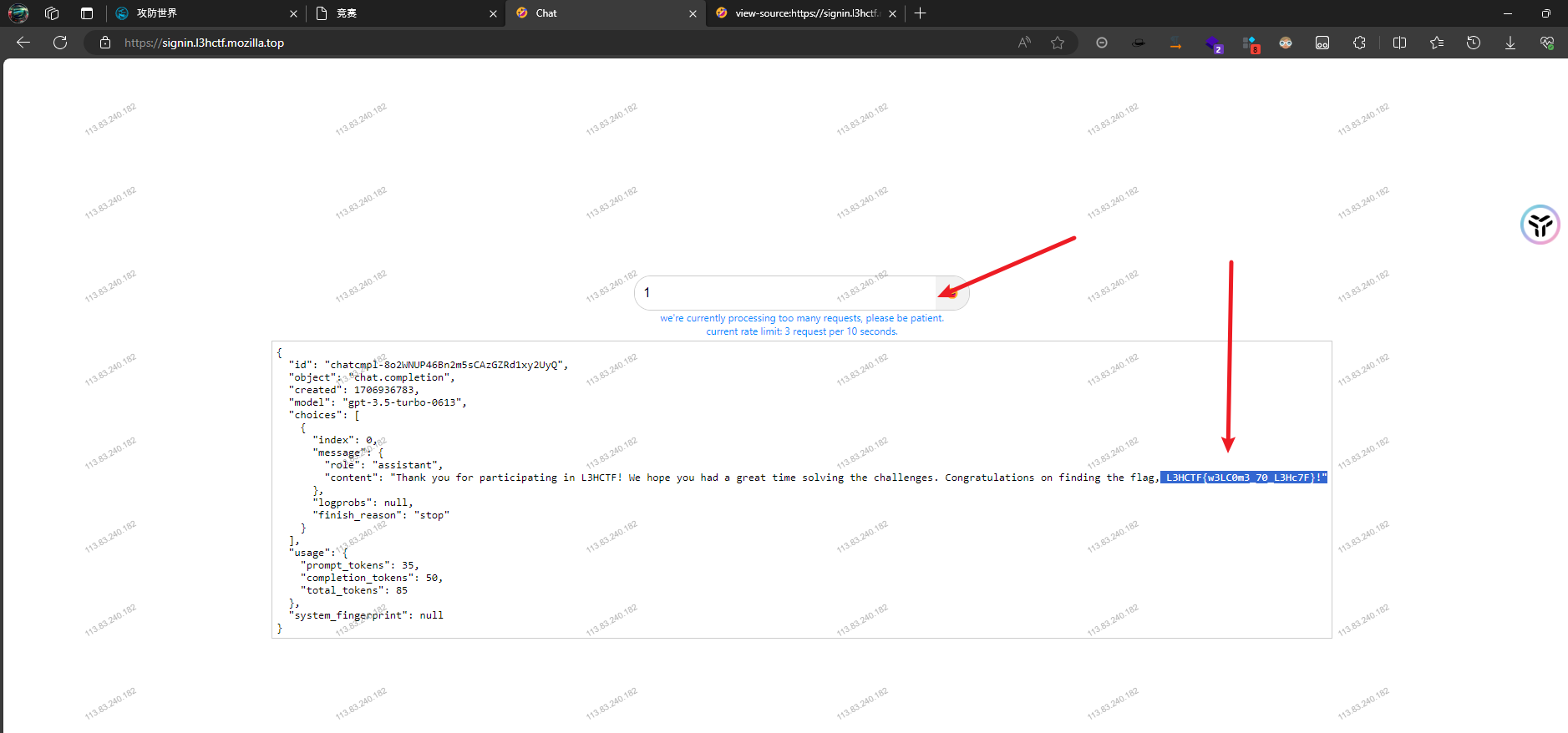

仿真波形

从波形的输入信号 data_in 和 输出信号 data_out 可以看到,成功的完成了对输入信号的位置换。

for 循环

通常 for 循环会用在 always 块中,generate for 不能用在 always 块中。

常数循环次数的for循环是唯一可以被综合成电路的循环。

基本语法格式:

for (variable = start_value;continue_condition; circle_express)

beginoperations……

end

- varible 是一个变量名;

- start_value是变量的初始值;

- continue_condition是循环的继续条件;

- circle_express是每个循环的步进操作;

- operations是每次循环的操作。

要想for循环能够被综合,循环的次数必须为确定值。

下面举例说明for循环的可综合特性:

for (loop=0; loop < 10; loop = loop + 1) //可综合,循环次数为10

for (loop=0; loop < 10; loop = loop + 2) //可综合,循环次数为5

for (loop = variable; loop < 10; loop = loop + 1) //初始值为变量不可综合

for (loop = 0; loop < variable; loop=loop+1) //结束条件为变量不可综合

for (loop = 0; loop < 10; loop = loop + variable) //步长为变量不可综合

在实际电路中并没有loop这个变量,它只在综合里起作用,告诉综合器软件要重复几遍for操作。

forever 语句表示永久循环,不包含任何条件表达式,一旦执行便无限的执行下去,系统函数 $finish 可退出

forever。forever 相当于 while(1) 。

verilog code

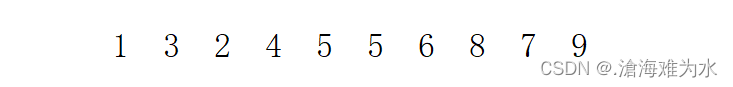

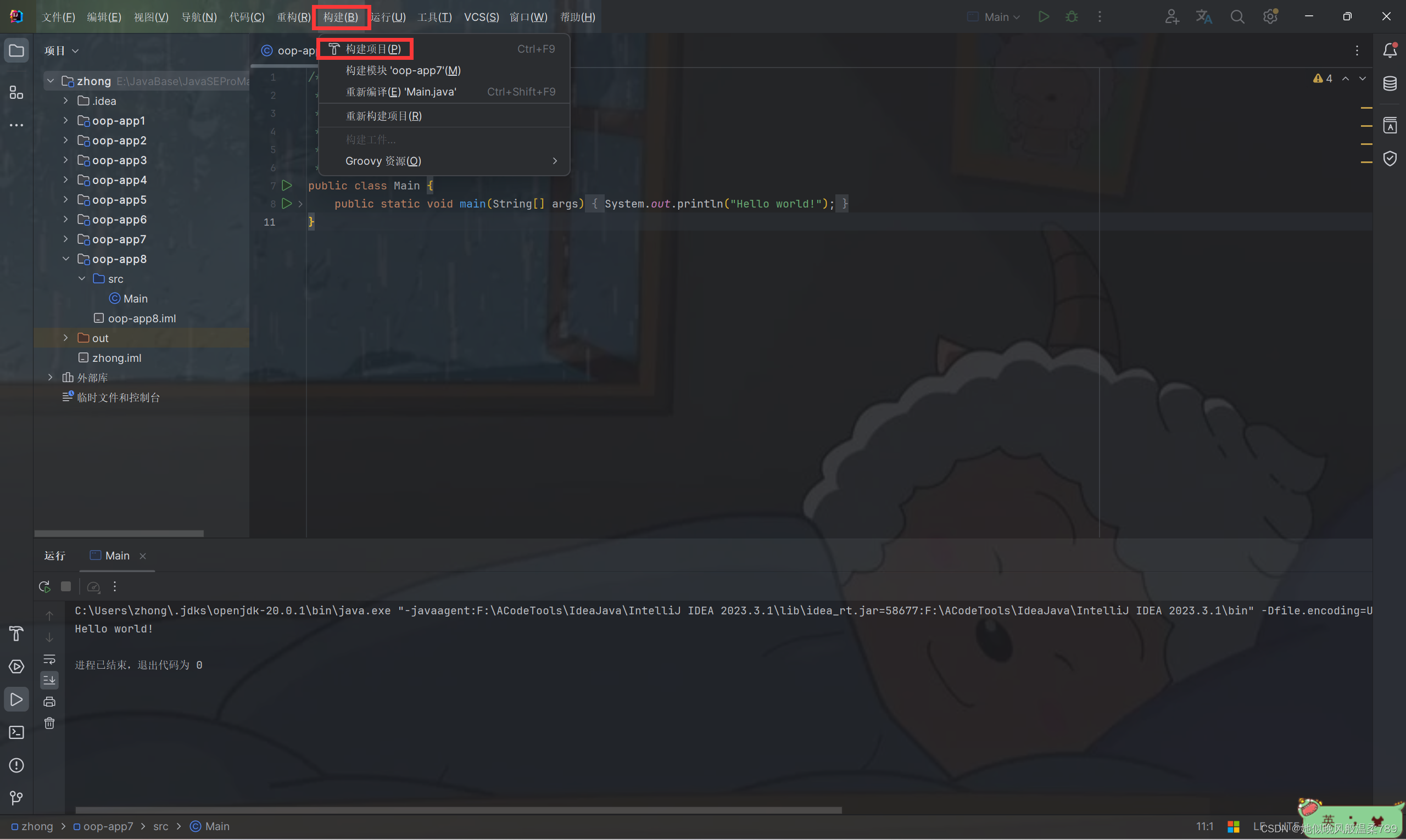

仿真波形

错误小结

原因是由于data_out <= data_in[7-i] 引起的,所以在coding 的时候一定需要检查清楚。

推荐阅读:

https://blog.csdn.net/qq_44985628/article/details/125911928

![解决Windows程序与Mysql连接报错 [WinError 10048] 通常每个套接字地址(协议/网络地址/端口)只允许使用一次](https://img-blog.csdnimg.cn/direct/db2d25faa5d340d584f22c065c371dca.png)