第1章 Verilog的基础知识

1.1 硬件描述语言HDL

硬件描述语言(HDL,hardware description language)是一种用形式化方法来描述数字电路和系统的语言。

设计者使用HDL设计数字系统后,通过电子设计自动化工具(EDA)仿真验证、通过自动综合工具转换成成门级电路网表、自动布局布线工具把网表转换为具体电路布线结构。

在制成物理器件之前,还可以用 Verilog 的门级模型(原语元件或UDP)来代替具体基本元件。

1.2 Verilog HDL的历史

1.3 Verilog HDL和VHDL的比较

VHDL:军方开发

Verilog HDL:民用转化

1.4 Verilog的应用情况和适用的设计

Verilog 适合系统级(system)、算法级(algorithem)、寄存器传输级(RTL)、逻辑级(logic)、门级(gate)、电路开关级(switch)设计,而 Sstem Verilog 是 Verilog 语言的护展和延伸,更适用于可重用的可综合 IP 和可重用的验证用 IP 设计,以及特大型(千万门级以上)基于IP的系统级设计和验证。

1.5 采用Verilog HDL设计复杂数字电路的优点

传统的设计方法需要根据电路原理图,人为手工布线。

Verilog HDL设计法更标准化:信号位数易改变,以适应不同规模的应用;Verilog HDL综合器生成的数字逻辑是一种标准的电子设计互换格式(EDIF)文件,独立于所采用的实现工艺。

把功能经过验证的、可综合的、实现后电路结构总门数在5000门以上的Verilog HDL模型称为“软核”(Soft Core)。把由软核构成的器件称为虚拟器件。

把在某一种现场可编程门阵列(FPGA)器件上实现的、经检验证明是正确的、总门数在5000 门以上电路结构编码文件称为“固核”(firm core)。

把在某一种专用集成电路工艺的(ASIC)器件上实现的、经检验证明是正确的、总门数在5000 门以上的电路结构版图掩膜称为“硬核” Chard core)。

在具体实现手段和工艺技术尚未确定的逻辑设计阶段,软核具有最大的灵活性。

1.6 采用硬件描述语言(Verilog HDL)的设计流程简介

1.6.1 自顶向下(Top_Down)设计的基本概念

1.6.2 层次管理的基本概念

设计树上,节点对应着该层次上基本单元的行为描述,树枝对应着基本单元的结构分解。

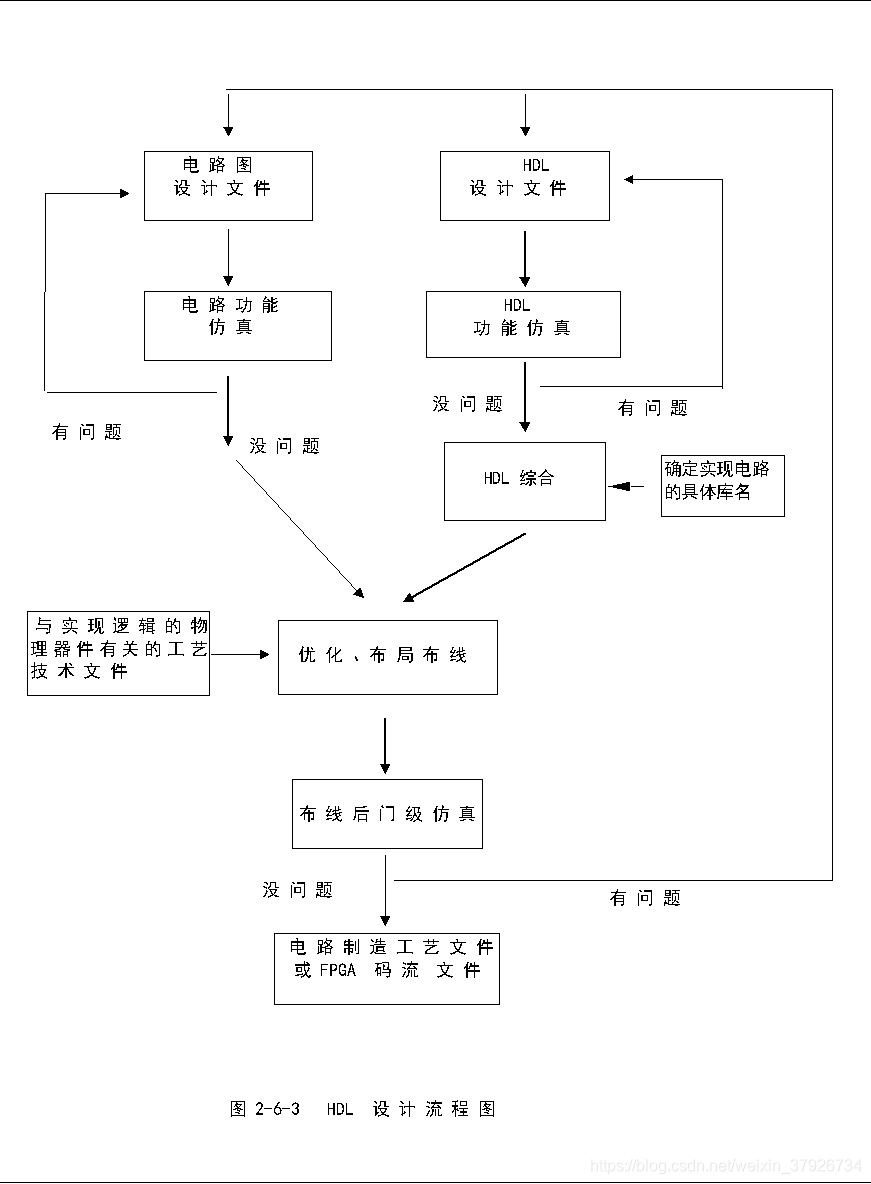

1.6.3 具体模块的设计编译和仿真的过程

在高层次上往在编写一些行为级的模块可以通过仿真加以验证,其主要目的是系统性能的总体考虑和各模块的指标分配,并非具体电路的实现,因而综合及其以后的步骤往往不需要进行。

而当设计的层次比较接近底层时,行为描述往往需要用电路逻辑来实现。这时的模块不仅需要通过仿真加以验证,还需进行综合、优化、布线和后仿真。总之具体电路是从底向上逐生实现的。

模块设计流程主要由两大主要功能部分组成:

(1)设计开发,即从编写设计文件 -> 综合到布局布线 -> 电路生成这样一系列步骤。

(2)设计验证,也就是进行各种仿真的一系列生骤,如果在仿真过程中发现问题就返回设计输入进行修改。