嵌入式开发Verilog教程(二)——Verilog HDL设计方法概述

嵌入式开发Verilog教程(二)——Verilog HDL设计方法概述

- 前言

- 一、Verilog HDL语言简介

- 1.1 Verilog HDL语言是什么

- 1.2 Verilog HDL设计复杂数字电路的优点

- 1.2.1 传统设计方法——电路原理图输入法

- 1.2.2 Verilog HDL设计方法与传统设计方法相比较的优势

- 1.2.3 Verilog HDL的标准化与软核的重用

- 1.2.4 软核、固核和硬核的概念以及它们的重用

- 二、采用硬件描述语言(Verilog HDL)的设计流程

- 2.1 自顶向下(Top-Down)设计的基本概念

- 2.2 具体模块的设计编译与仿真的过程

前言

- 在数字逻辑设计领域,迫切需要一种共同的工业标准来统一对数字逻辑电路及系统的描述,这样就能把系统设计工作分解为逻辑设计(前端)和电路实现(后端)两个互相独立而又相关的部分。由于逻辑设计的相对独立性就可以把专家们设计的各种常用数字逻辑电路和系统部件(如FFT算法、DCT算法部件)建成宏单元(Megcell)或软核(Soft-Core)库供设计者引用,以减少重复劳动,提高工作效率。电路的实现则可借助于综合工具和布局布线工具(与具体工艺技术有关)来自动地完成。

- 硬件描述语言(HDL)是一种用形式化方法(学术专业术语)来描述数字电路和设计数字逻辑系统的语言。它可以使数字逻辑电路设计者利用这种语言来描述自己的设计思想,然后利用电子设计自动化(简称为EDA)工具进行仿真,再自动综合到门级电路,再用ASIC或FPGA实现其功能。这种设计方法也被称为高层次设计(High-Level-Design)的方法。

一、Verilog HDL语言简介

1.1 Verilog HDL语言是什么

- Verilog HDL是硬件描述语言的一种,用于数字电子系统设计。设计人员可以用它实现各种级别的逻辑设计,并且可以用它进行系统级(System)、算法级(Alogrithem)、寄存器传输级(RTL)、逻辑级(Logic)、门级(Gate)、电路开关级(Switch)设计。

- 硬件描述语言(HDL)是一种用形式化方法(学术专业术语)来描述数字电路和设计数字逻辑系统的语言。它可以使数字逻辑电路设计者利用这种语言来描述自己的设计思想,然后利用电子设计自动化(简称为EDA)工具进行仿真,再自动综合到门级电路,再用ASIC或FPGA实现其功能。这种设计方法也被称为高层次设计(High-Level-Design)的方法。

1.2 Verilog HDL设计复杂数字电路的优点

1.2.1 传统设计方法——电路原理图输入法

- 几十年前,当时所做的复杂数字逻辑电路及系统的设计规模比较小也比较简单,其中所用到的FPGA或ASIC设计工作往往只能采用厂家提供的专用电路图输入工具来进行。为了满足设计性能指标,工程师往往需要花好几天或更长的时间进行艰苦的手工布线。工程师还得非常熟悉所选器件的内部结构和外部引线特点,才能达到设计要求。这种低水平的设计方法大大延长了设计周期。

- 近年来,FPGA和ASIC的设计在规模和复杂度方面不断取得进展,而对逻辑电路及系统的设计的时间要求却越来越短。这些因素促使设计人员采用高水准的设计工具,如:硬件描述语言(Verilog HDL或VHDL)来进行设计。

1.2.2 Verilog HDL设计方法与传统设计方法相比较的优势

- 采用电路原理图输入法进行设计,具有设计的周期长,需要专门的设计工具,需手工布线等缺陷。而采用Verilog HDL输入法时,由于Verilog HDL的标准化,可以很容易地把完成的设计移植到不同的厂家的不同的芯片中去,并在不同规模应用时可以较容易地作修改。这不仅是因为用Verilog HDL所完成的设计,它的信号位数是很容易改变的,可以很容易地对它进行修改,来适应不同规模的应用,在仿真验证时,仿真测试矢量还可以用同一种描述语言来完成,而且还因为采用Verilog HDL综合器生成的数字逻辑是一种标准的电子设计互换格式(EDIF)文件,独立于所采用的实现工艺。有关工艺参数的描述可以通过 Verilog HDL提供的属性包括进去,然后利用不同厂家的布局布线工具,在不同工艺的芯片上实现。

- 采用Verilog HDL输入法最大的优点是其与工艺无关性。这使得工程师在功能设计、逻辑验证阶段,可以不必过多考虑门级及工艺实现的具体细节,只需要利用系统设计时对芯片的要求,施加不同的约束条件,即可设计出实际电路。实际上这是利用了计算机的巨大能力在EDA工具的帮助下,把逻辑验证与具体工艺库匹配、布线及时延计算分成不同的阶段来实现从而减轻了人们的繁琐劳动。

1.2.3 Verilog HDL的标准化与软核的重用

- 由于Verilog HDL设计方法的与工艺无关性,因而大大提高了Verilog HDL模型的可重用性。而这正是由于Verilog HDL的标准化大大加快了Verilog HDL的推广和发展。下面介绍一个非常重要的概念软核:

- 将功能经过验证的、可综合的、实现后电路结构总门数在5000门以上的Verilog HDL模型称之为“软核”(Soft Core)。

- 而把由软核构成的器件称为虚拟器件,在新电路的研制过程中,软核和虚拟器件可以很容易地借助EDA综合工具与其它外部逻辑结合为一体。这样,软核和虚拟器件的重用性就可大大缩短设计周期,加快了复杂电路的设计。

1.2.4 软核、固核和硬核的概念以及它们的重用

- 与软核相对应的是固核(Firm Core)与硬核(Hard Core)的概念:

- (1)“固核”:在某一种现场可编程门阵列(FPGA)器件上实现的,经验证是正确的总门数在5000门以上电路结构编码文件;

- (2)“硬核”:把在某一种专用半导体集成电路工艺的(ASIC)器件上实现的经验证是正确的总门数在5000门以上的电路结构掩膜。

- 综上,相比较于固核与硬核,在具体实现手段和工艺技术尚未确定的逻辑设计阶段,软核具有最大的灵活性,它可以很容易地借助EDA综合工具与其它外部逻辑结合为一体。近年来电路实现工艺技术的发展是相当迅速的,为了逻辑电路设计成果的积累,和更快更好地设计更大规模的电路,发展软核的设计和推广软核的重用技术是非常有必要的。

二、采用硬件描述语言(Verilog HDL)的设计流程

2.1 自顶向下(Top-Down)设计的基本概念

- 有序现代集成电路制造工艺技术的快速发展,一块芯片通常集成数十乃至数百万个器件,同时也使得一个工程师难以设计如此大规律的电路。因此,利用层次化、结构化的设计方法,一个完整的硬件设计任务首先由总设计师划分为若干个可操作的模块,编制出相应的模型(行为的或结构的),通过仿真加以验证后,再把这些模块分配给下一层的设计师,这就允许多个设计者同时设计一个硬件系统中的不同模块,其中每个设计者负责自己所承担的部分;而由上一层设计师对其下层设计者完成的设计用行为级上层模块对其所做的设计进行验证。自顶向下的设计思想如下图所示:

- 自顶向下的设计(即TOP_DOWN设计)是从系统级开始,把系统划分为基本单元,然后再把每个基本单元划分为下一层次的基本单元,一直这样做下去,直到可以直接用EDA元件库中的元件来实现为止。在实际项目开发中,先进行方案的总体论证、功能描述、任务和指标的分配。随着系统变得复杂和庞大,特别需要在样机问世之前,对产品的全貌有一定的预见性。目前,EDA技术的发展使得设计师有可能实现真正的自顶向下的设计。

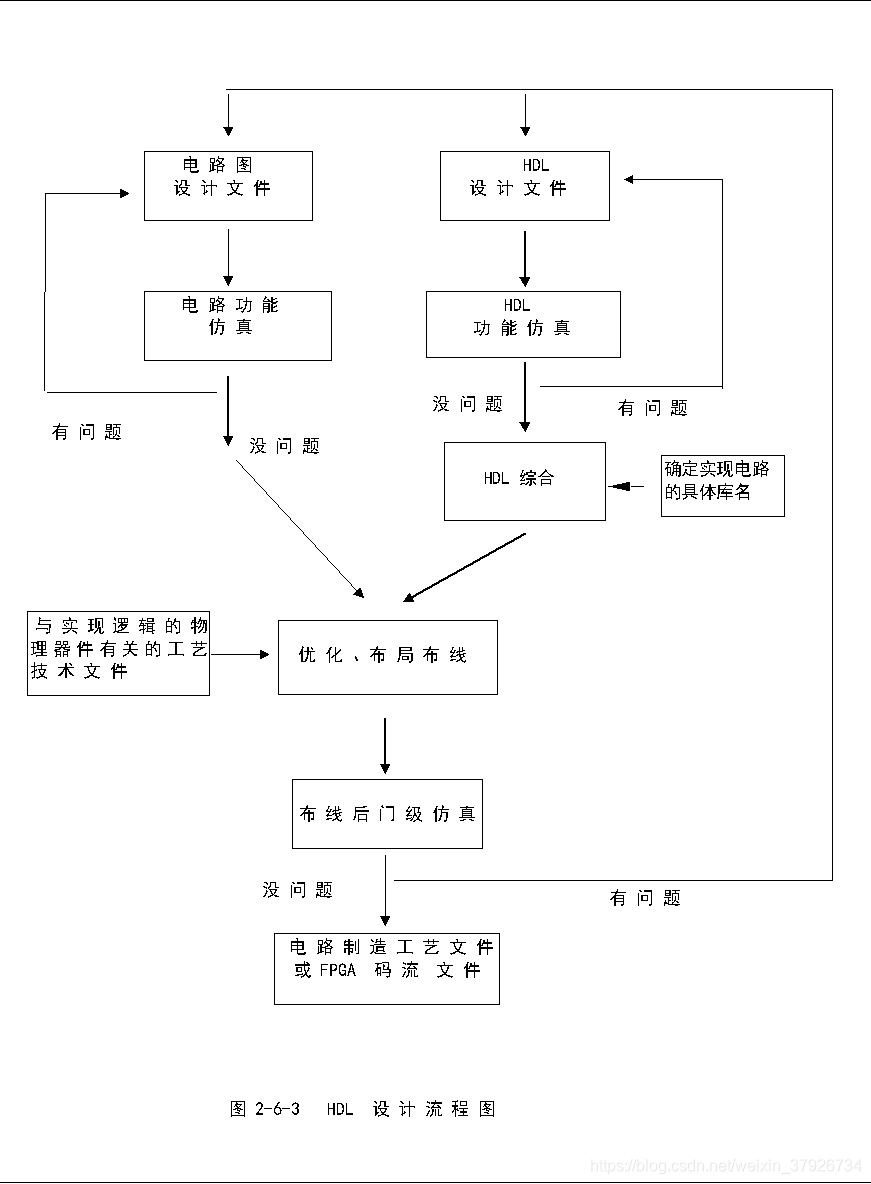

2.2 具体模块的设计编译与仿真的过程

- 在不同的层次做具体模块的设计所用的方法也有所不同,在高层次上往往编写一些行为级的模块通过仿真加以验证,其主要目的是系统性能的总体考虑和各模块的指标分配,并非具体电路的实现。而当设计的层次比较接近底层时行为描述往往需要用电路逻辑来实现,这时的模块不仅需要通过仿真加以验证,还需进行综合、优化、布线和后仿真。EDA工具往往不仅支持HDL描述也支持电路图输入,有效地利用这两种方法是提高设计效率的办法之一。下面的流程图简要地说明了模块的编译和测试过程:

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如若转载,请注明出处:http://xiahunao.cn/news/254233.html

如若内容造成侵权/违法违规/事实不符,请联系瞎胡闹网进行投诉反馈,一经查实,立即删除!

![[蓝桥杯/java/算法]A——隔行变色](https://img-blog.csdnimg.cn/579f974ec4874d9fa1464050b893190d.png)