1. 传输速率与带宽的关系

当我们谈论PCIe总线标准的传输速率时,我们使用GT/s(Giga Transfers per second,千兆传输/秒)来衡量,而不是Gbps(Giga Bits Per Second,千兆位/秒)。这是因为传输速率是基于物理层通信协议的属性,与链路宽度等因素无关。

PCIe总线的吞吐量(可用带宽)可以通过以下公式计算:

吞吐量 = 传输速率 * 编码方案

例如,PCIe 2.0协议支持5.0 GT/s,每个Lane上每秒传输5G个bit。然而,并不是每个Lane都支持5Gbps的速率,因为PCIe 2.0采用的是8b/10b编码方案。这意味着每传输8个bit需要发送10个bit。

因此,PCIe 2.0协议的每个Lane支持的速率为 5 GT/s * 8 / 10 = 4 Gbps = 500 MB/s。

举个例子,对于一个PCIe 2.0 x8通道,可用带宽为 4 Gbps * 8 = 32 Gbps = 4 GB/s。

同样地,PCIe 3.0协议支持8.0 GT/s,每个Lane上每秒传输8G个bit。然而,PCIe 3.0采用的是128b/130b编码方案,即每传输128个bit需要发送130个bit。

因此,PCIe 3.0协议的每个Lane支持的速率为 8 GT/s * 128 / 130 = 7.877 Gbps = 984.6 MB/s。

举个例子,对于一个PCIe 3.0 x16通道,可用带宽为 7.877 Gbps * 16 = 126.031 Gbps = 15.754 GB/s。

2. PCI Express Fabric拓扑结构

一个PCI Express Fabric由点对点的Link组成,用于连接一组组件。下图展示了一个例子PCI Express Fabric的拓扑结构。这个图展示了一个单一的PCI Express Fabric实例,也称为层次结构,由一个根复杂器(Root Complex)、多个端点(I/O设备)、一个交换机和一个PCI Express到PCI/PCI-X桥接器组成,它们通过PCI Express Link相互连接。

1.Root Complex

Root Complex(根复杂器)是PCI Express总线架构中的一个重要组成部分,它是连接CPU和内存子系统与PCI Express设备之间的桥梁。Root Complex通常由一个或多个PCI Express端口组成,每个端口连接到一个或多个PCI Express设备,形成一个I/O层次结构。Root Complex还负责管理PCI Express总线的配置和控制,包括分配总线带宽、处理传输错误、管理电源管理和热插拔等功能。

在PCI Express架构中,Root Complex是一个逻辑实体,可以由一个芯片组或处理器集成电路实现。Root Complex可以支持多个PCI Express端口,每个端口可以连接到一个或多个PCI Express设备。PCI Express设备可以是端点设备或交换机设备,它们可以通过PCI Express总线进行通信和数据传输。

2.Endpoint

Endpoint(端点)是指在PCI Express总线架构中可以作为请求方或完成方的功能类型。它可以代表自身执行PCI Express事务,也可以代表一个独立的非PCI Express设备执行PCI Express事务。端点可以是传统端点、PCI Express端点或根复杂器集成端点(RCiEPs)。

传统端点是指符合传统PCI规范的设备,通过PCI Express到PCI桥接器与PCI Express总线连接。这些设备可以通过PCI Express总线进行通信和数据传输。

PCI Express端点是指符合PCI Express规范的设备,直接连接到PCI Express总线。这些设备可以通过PCI Express总线进行高速通信和数据传输。

根复杂器集成端点(RCiEPs)是指集成在根复杂器中的端点功能。它们可以作为根复杂器的一部分执行PCI Express事务,例如根复杂器集成的图形控制器或USB主机控制器。

总之,端点是PCI Express总线架构中的一种功能类型,可以作为请求方或完成方执行PCI Express事务,可以是传统端点、PCI Express端点或根复杂器集成端点。

3.Switch

PCIe交换机(PCIe Switch)是一种用于构建PCI Express(PCIe)总线拓扑结构的设备。它允许多个PCIe设备通过高速数据通道进行连接和通信。

PCIe交换机的主要功能是转发PCIe事务,类似于传统PCI总线上的PCI桥接器。它可以将来自一个PCIe设备的事务转发到另一个PCIe设备,实现设备之间的数据传输和通信。

PCIe交换机通常具有多个端口,每个端口可以连接一个PCIe设备。这些端口可以是上游端口(连接到其他交换机或主机)或下游端口(连接到终端设备或其他交换机的上游端口)。

通过使用PCIe交换机,可以构建复杂的PCIe拓扑结构,例如树状结构、星型结构或多级结构。这样可以实现多个设备之间的高速数据传输和通信,并提供更高的带宽和灵活性。

4.Root Complex Event Collector

Root Complex Event Collector(RCEC)是PCI Express(PCIe)架构中的一个组件,用于收集和处理与Root Complex相关的事件。

Root Complex是PCIe总线的起始点,它通常是主机或服务器系统中的PCIe控制器。Root Complex负责管理和控制整个PCIe拓扑结构,并与其他PCIe设备进行通信。

RCEC是Root Complex的一部分,它的主要功能是监控和收集与Root Complex相关的事件。这些事件可以包括连接和断开连接的设备、错误和异常情况、配置更改等。RCEC会记录这些事件,并根据需要采取相应的措施,例如通知主机系统或其他相关组件。

通过RCEC,系统可以实时监控PCIe总线上发生的事件,并及时采取必要的措施来处理这些事件。这有助于确保PCIe设备的正常运行和系统的稳定性。

5.PCI Express to PCI/PCI-X Bridge

PCI Express to PCI/PCI-X桥接器是一种设备,用于连接PCI Express(PCIe)总线和传统的PCI或PCI-X总线。它允许PCIe系统与PCI或PCI-X设备进行兼容性连接和通信。

PCIe to PCI/PCI-X桥接器的主要功能是将来自PCIe总线的事务转换为PCI或PCI-X事务,并将其传递给连接的PCI或PCI-X设备。它充当了PCIe和PCI/PCI-X之间的接口,使得PCIe系统能够与旧有的PCI或PCI-X设备进行互操作。

通过PCIe到PCI/PCI-X桥接器,PCIe系统可以利用现有的PCI或PCI-X设备,无需更换或升级这些设备。这对于需要使用旧有PCI或PCI-X设备的系统来说非常有用,例如在过渡期间或需要与遗留系统进行兼容性连接的情况下。

PCIe to PCI/PCI-X桥接器通常具有一个或多个PCI或PCI-X插槽,用于连接PCI或PCI-X设备。它还提供了必要的协议转换和信号适配,以确保PCIe和PCI/PCI-X之间的兼容性和互操作性。

3. post 和non_posted

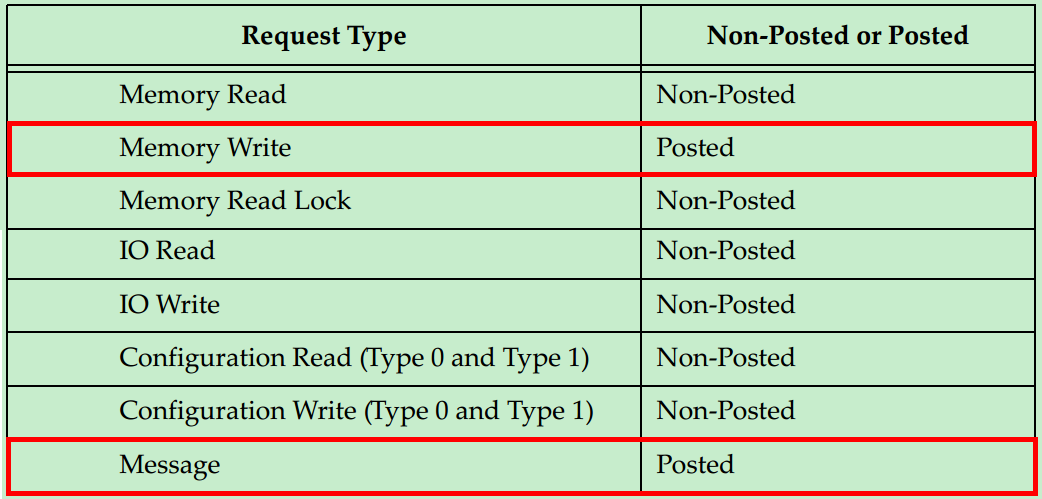

在介绍事务层之前,首先简单地了解一下PCIe总线的通信机制。假设某个设备要对另一个设备进行读取数据的操作,首先这个设备(称之为Requester)需要向另一个设备发送一个Request,然后另一个设备(称之为Completer)通过Completion Packet返回数据或者错误信息。在PCIe Spec中,规定了四种类型的请求(Request):Memory、IO、Configuration和Messages。其中,前三种都是从PCI/PCI-X总线中继承过来的,第四种Messages是PCIe新增加的类型。详细的信息如下表所示:

从表中我们可以发现,只有Memory Write和Message是Posted类型的,其他的都是Non-Posted类型的。所谓Non-posted,就是Requester发送了一个包含Request的包之后,必须要得到一个包含Completion的包的应答,这次传输才算结束,否则会进行等待。所谓Posted,就是Requester的请求并不需要Completer通过发送包含Completion的包进行应答,当然也就不需要进行等待了。很显然,Posted类型的操作对总线的利用率(效率)要远高于Non-Posted型。

那么为什么要分为Non-Posted和Posted两种类型呢?对于Memory Writes来说,对效率要求较高,因此采用了Posted的方式。但是这并不意味着Posted类型的操作完全不需要Completer进行应答,Completer仍然可采用另一种应答机制——Ack/Nak的机制(在数据链路层实现的)。

1.Posted传输

Posted总线事务是指PCI主设备向目标设备进行数据传输时,数据到达PCI桥后,由PCI桥接管来自上游总线的总线事务,并将其转发到下游总线,此时上游总线可释放。

使用这种数据传输方式,数据请求在通过PCI总线后,就可以逐级释放总线资源。

下面以DMA写操作为例,说明PCI的Posted传输(DMA操作即PCI设备主动对系统存储器进行操作)。

PCI设备11向主存储器写数据:

首先PC设备11将主存储器写请求发向PCI总线x1,注意这个写请求使用的地址是PCI总线域的地址。

PCI总线x1上的所有设备监听这个请求,因为PCI设备11是向处理器的存储器写数据,所以PCI总线x1上的 PCI Agent都不会接收这个数据请求。

PCI桥x1发现当前总线事务使用的PCI总线地址不是其下游设备使用的PCI总线地址,则接收这个请求,并结束来自PCI设备11的 Posted存储器写请求,将这个数据请求推到上游PCI总线上,即PCI总线x0。

PCI总线x0上的所有设备包括HOST主桥将监听这个请求,PCI总线x0上的PCI设备也不会接收这个请求,此时这个数据请求由HOST主桥x接收,并结束PCI桥x1的Posted存储器写请求。

HOST主桥x发现这个数据请求发向存储器,则将来自PCI总线x0的PCI总线地址转换为存储器域地址,通过存储器控制器将数据写入存储器,完成PCI设备11的DMA写操作(没有完成报文)。

2.Non-Posted传输

Non-Posted总线事务是指PCI主设备向目标设备进行数据传输时,数据必须到达最终目的地后才能结束当前事务总线的传输方式。PCI总线在没有结束当前总线事务时必须等待传输完成,不会释放总线资源。

这种等待将严重阻塞当前的PCI总线的其他数据传送。因此在PCI总线中使用Delayed方式完成Non-Posted,在PCIe总线中使用Split方式完成 Non-Posted总线事务。

PCI设备进行DMA读与DMA写过程类似,不过存储器读总线事务是使用Non-Posted总线事务。

PCI设备11向主存储器读数据:

首先PCI设备11将存储器读请求发向PCI总线x1。

PCI总线x1上的所有设备监听这个请求,因为PCI设备11是从存储器中读取数据,所以PCI总线x1上的设备不会接收这个请求。PCI桥x1发现下游PCI总线没有设备接收,则接收这个数据请求,并将它推到上游PCI总线上,即PCI总线x0上。

PCI总线x0上的设备监听这个请求,也不会接受这个数据请求,最后这个数据请求被HOST主桥x接收。

HOST主桥发现这个数据请求是发向主存储器的,则将PCI总线x0的PCI总线地址转为存储器地址,之后通过控制器将数据读出,带着读完成信息转发到HOST主桥x。

HOST主桥x将这个带数据的读完成事务经由PCI桥x1传递到PCI设备11,设备11接收到这个数据后结束DMA读(有完成报文)。

在上述Non-Posted总线事务中,只有读完成依次通过PCI总线x1和x0后,存储器读总线事务才不继续占用PCI总线x1和x0的资源。可以发现这种传输并不合理,PCI总线为了解决这个总线拥塞问题,使用Delayed传输方式。

4. PCIe拓扑结构

PCIe拓扑结构是一个树形结构.

主要包括Root Complex, Switch, PCIe Bridge.

Root Complex

Root Complex(RC)是树的根,它为CPU代言,与整个计算机系统其他部分通信,比如CPU通过它访问内存,通过它访问PCIe系统中的设备.

Root Complex: A Root Complex (RC) denotes the root of an I/O hierarchy that connects the CPU/memory subsystem to the I/O.

Switch

Switch由一个上游端口(Upstream Port)和2~n个下游端口(Downstream Port)组成.

Switch的作用就是扩展PCIe端口,并为挂在它上面的设备(Endpoint或者Switch)提供路由和转发服务.

每个Switch内部,也是有一根内部PCIe总线的,然后通过若干个Bridge,扩展出若干个下游端口

从系统配置软件看,Switch内部由多个虚拟PCI-to-PCI桥组成. Switch内部上游和下游端口都对应一个PCI-to-PCI桥,每个桥都有PCI配置空间. 在Switch内部还有一条虚拟的PCI总线,用来连接每个虚拟PCI桥.

To configuration software, a Switch appears as a collection of virtual PCI-to-PCI Bridges.

Switches: A Switch is defined as a logical assembly of multiple virtual PCI-to-PCI Bridge devices. A Switch may have several Downstream Ports but can only have one Upstream Port. Switches provide a fanout or aggregation capability and allow more devices to be attached to a single PCIe Port. They act as packet routers and recognize which path a given packet will need to take based on its address or other routing

information.

Bridge

Bridge provides an interface to other buses, such as PCI or PCI‐X, or even another PCIe bus.

Bridge is a function that virtually or actually connects a PCI/PCI-X segment or PCI Express Port with an internal component interconnect or with another PCI/PCI-X bus segment or PCI Express Port.

PCIe bridge 可以将PCIe总线转换成PCI总线,用于连接PCI设备。

PCIe bridge 可以将PCI总线转换成PCIe总线(Reverse Bridge),用于连接PCIe设备。

Endpoint

Endpoints: Endpoints are devices in a PCIe topology that are not Switches or bridges and act as initiators or Completers of transactions on the bus. They reside at the bottom of the branches of the tree topology and only implement a single Upstream Port (facing toward the Root).

Endpoint refers to a type of Function that can be the Requester or Completer of a PCI Express transaction either on its own behalf or on behalf of a distinct non-PCI Express device.

PCIe Buses

Up to 256 Bus Numbers can be assigned by configuration software. The initial Bus Number, Bus 0, is typically assigned by hardware to the Root Complex. Bus 0 consists of a Virtual PCI bus with integrated endpoints and Virtual PCI‐to‐PCI Bridges (P2P) which are hard‐coded with a Device number and Function number.

Configuration software begins the process of assigning bus numbers by searching for bridges starting with Bus 0, Device 0, Function 0. When a bridge is found, software(depth first search) assigns the new bus a bus number that is unique and larger than the bus number the bridge lives on.

PCIe Devices

PCIe permits up to 32 device attachments on a single PCI bus, however, the point‐to‐point nature of PCIe means only a single device can be attached directly to a PCIe link and that device will always end up being Device 0.

PCIe functions

PCIe contains up to 8 functions that all share the bus interface for that device, numbered 0‐7.Devices that have multiple Functions do not need to be implemented sequentially.