视频链接

USB3.0 HUB电路设计

第34课------USB电路设计基础

第36课------USB 2.0 HUB电路设计

第38课------USB 3.0电路设计

第40课------Type-C电路设计

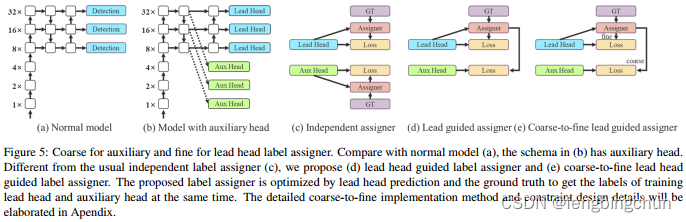

1、USB HUB基本介绍

USB Hub,指的是一种可以将一个USB接口扩展为多个,并可以使这些接口同时使用的装置。

USB 3.0 HUB的特点:

1、可将一个USB接口扩展成多个独立工作的USB接口

2、直接与电脑相连, 无须外接电源,简单好用

3、电脑自动识别安装, 无须驱动程序,即插即用,插拔自如

4、内置电流过载短路保护装置

5、支持USB3.0,向下兼容USB2.0

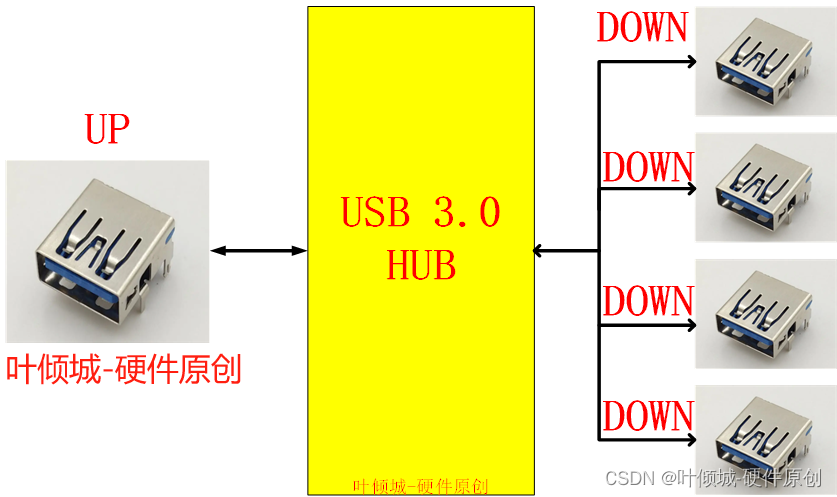

// USB 3.0 type-A管脚定义

USB 3.0 type-A管脚定义

| 引脚 | A管脚定义 | 线缆颜色 | 描述 |

| 1 | VBUS | 红色 | 5V供电 |

| 2 | D- | 白色 | 2.0数据差分对 |

| 3 | D+ | 绿色 | |

| 4 | GND | 黑色 | 电源地 |

| 5 | StdA_SSRX- | 蓝色 | 3.0高速数据差分对 |

| 6 | StdA_SSRX+ | 黄色 | |

| 7 | GND_DRAIN | N/A | 信号地 用于降低噪声干扰 |

| 8 | StdA_SSTX- | 紫色 | 3.0高速数据差分对 |

| 9 | StdA_SSTX+ | 橙色 |

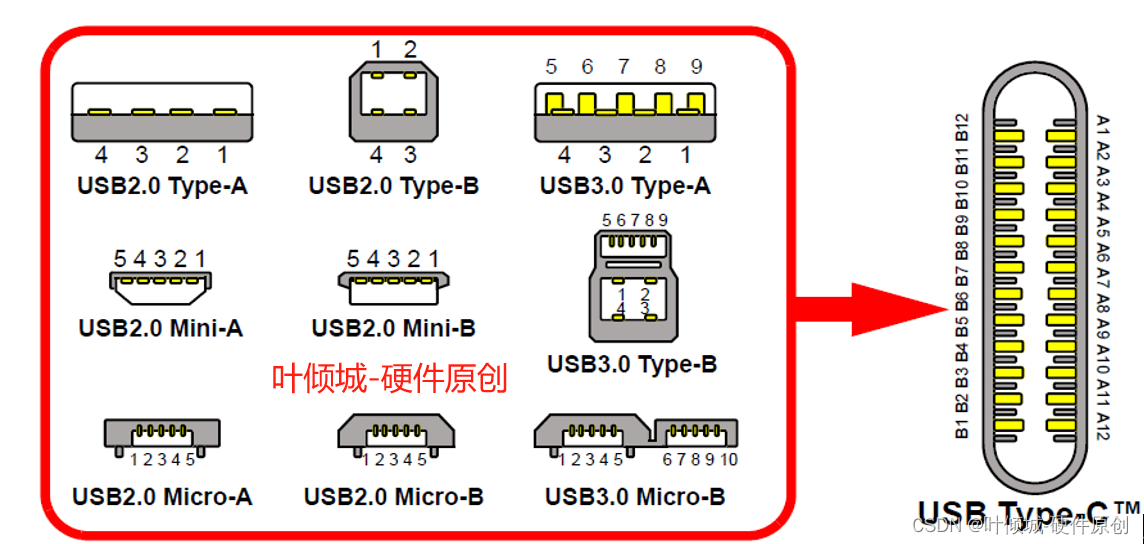

// type-C管脚定义

| 功能 | 引脚 | 描述 |

| USB3 | A2,A3,B2,B3,A10,A11,B10,B11 | USB3数据传输 |

| USB2.0 | A6/B6(D+),A7/B7(D-) | USB2.0数据传输 |

| 配置 | CC1,CC2 | 配置功能接口,插拔检测,供电协议信息传输,Vconn功能 |

| 辅助信号 | SBU1,SBU2 | 辅助信号 |

| 供电 | VBus,Vconn,GND | 供电 |

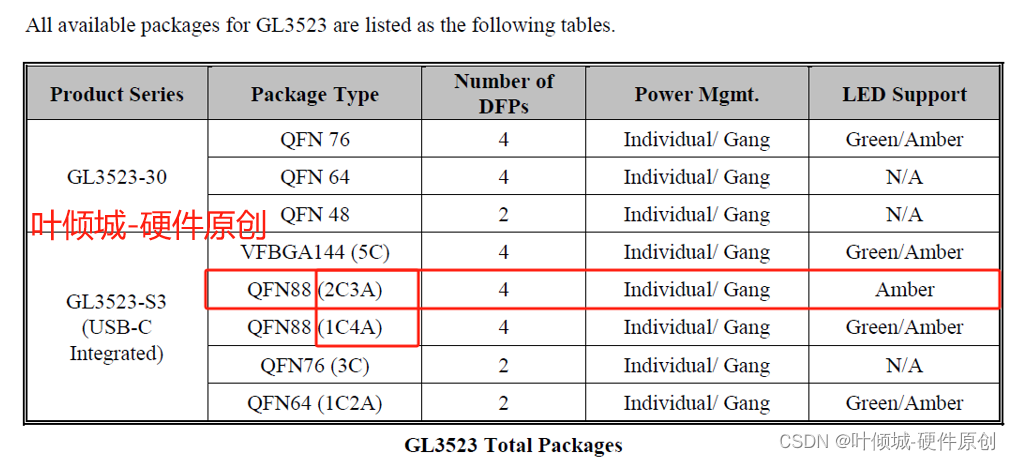

2、(创惟)GL3523-S ; USB3.2 GEN1一拖四 (★)

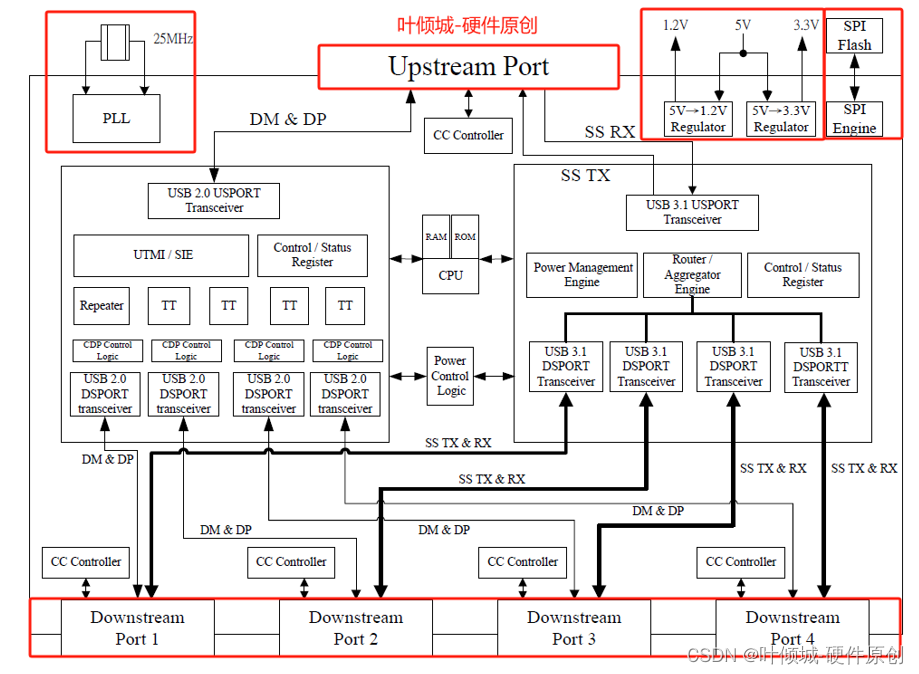

Genesys GL3523是一款4端口、低功耗、可配置的集线器控制器。

它符合USB 3.1规范。GL3523集成Genesys Logic自主研发的USB 3.1 Gen 1超高速发射器/接收器物理层(PHY)和USB 2.0高速PHY。

它支持Super Speed、Hi-Speed和全速USB连接,并完全向后兼容所有USB 2.0和USB 1.1主机。

GL3523 family

2.1、结构及功能框图

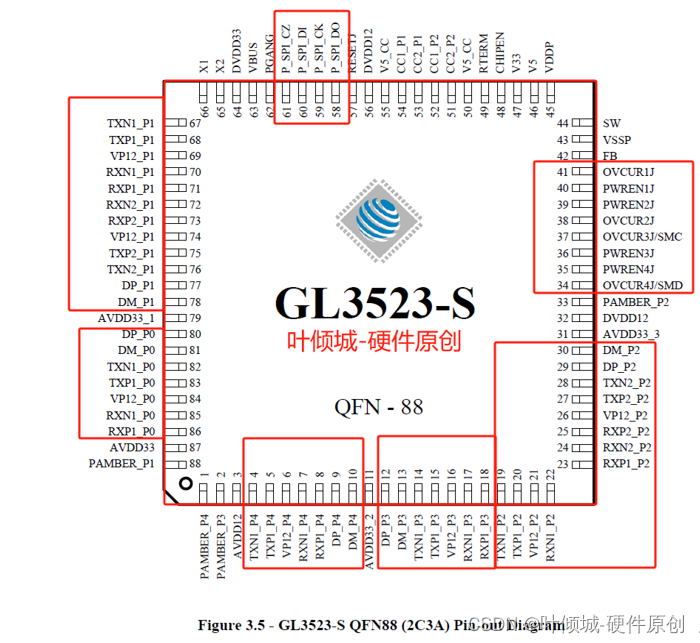

2.2、管脚定义(GL3523-S-QFN88 2C3A)

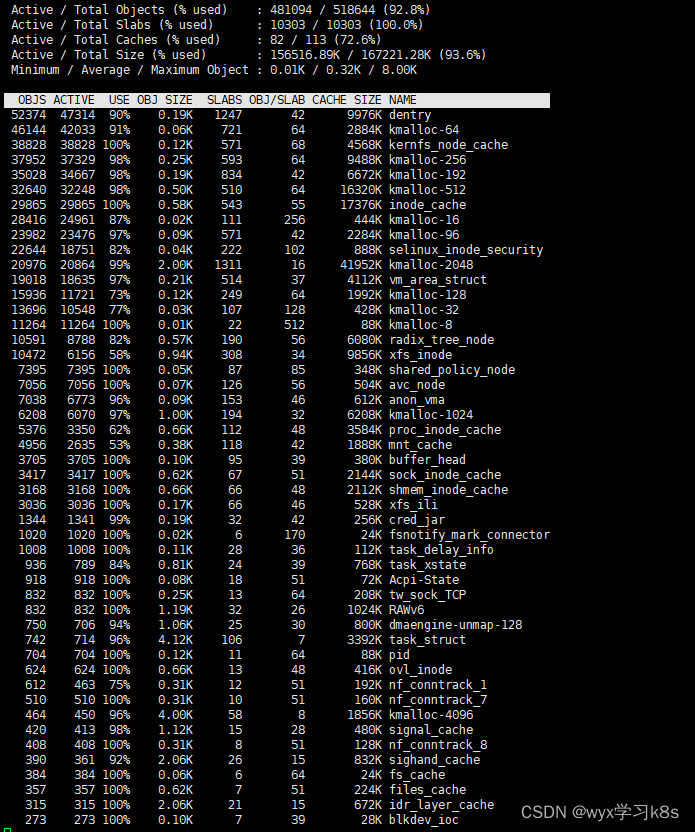

2.2.1、Power & Switching Regulator (20 + 4 = 24 PIN)

| 管脚名 | 描述 |

| VP12_P0~4/AVDD12 | 模拟1.2V |

| AVDD12 | 数字1.2V |

| DVDD33 | 数字3.3V |

| AVDD33 | 模拟3.3V |

| VBUS | 有效输入的VBUS检测引脚 |

| V33 | 5V至3.3V稳压器Vout和3.3输入 |

| V5 | 5V电源输入。如果使用外部3.3V稳压器,应连接到V33 |

| V5_CC | CC的5V电源输入。它必须提供5V来使用CC功能。 |

| 管脚符号 | 管脚号 | 类型 | Switching regulator(5V to 1.2V) |

| FB | 42 | A | Feedback sense, output 1.2V |

| SW | 44 | A | Internal switches output. Connect this pin to the output inductor |

| VDDP | 45 | P | Dedicated 5V power input for embedded switching regulator |

| VSSP | 43 | P | Dedicated Ground for embedded switching regulator |

2.2.2、USB Interface(38 PIN)

USB 2.0 & USB 3.1收发器

2.2.3、Type-C Interface(4 PIN 注意P1 & P2)

2.2.4、Hub Interface (13 PIN)

| 管脚符号 | 管脚号 | 类型 | 描述 |

| PAMBER_ P1~4 | 88,33, 2,1 | B | Amber LED indicator for DSPORT1~4 |

| PWREN 1~4J | 40,39, 36,35 | B | Active low. Power enable output for DSPORT1~4 PWREN1# is the only power-enable output for GANG mode. |

| OVCUR 1~4J | 41,38, 37,34 | I (pd) | Active low. Over current indicator for DSPORT1~4 The OVCUR pin of DFP1 will be the only over-current flag for GANG mode. ●In reset state : OVCUR3J will be SMC, OVCUR4J will be SMD ●SMBUS function is only available in VFBGA144 and QFN88 |

| PGANG | 62 | I | Default put in input mode after power-on reset. Individual/gang mode is strapped during this period. |

2.2.5、Clock and Reset Interface (4 PIN)

| 管脚符号 | 管脚号 | 类型 | 描述 |

| X1 | 66 | I | Crystal / OSC clock input |

| X2 | 65 | O | Crystal clock output. |

| RESETJ | 57 | I | Active low. External reset input, default pull high 10KΩ. When RESET# = low, whole chip is reset to the initial state. 低有效。外部复位输入,默认拉高10KΩ。 当RESET#=低,整个芯片复位到初始状态。 |

| CHIPEN | 48 | I (pu) | 0: Disable whole chip and keep hub in lowest power state (standby mode) 1: Normal state 0:禁用整个芯片并保持集线器处于最低功率状态(待机模式) 1:正常状态 |

2.2.6、SPI Interface (4 PIN)

2.2.7、Miscellaneous Interface (1 PIN)

| 管脚符号 | 管脚号 | 类型 | 描述 |

| RTERM | 49 | A (analog) | A 20Kohm resister must be connected between RTERM and Ground RTERM和地之间必须连接20Kohm电阻 |

24+38+4+13+4+4+1=88 PIN

2.3、GL3523-S设计注意事项

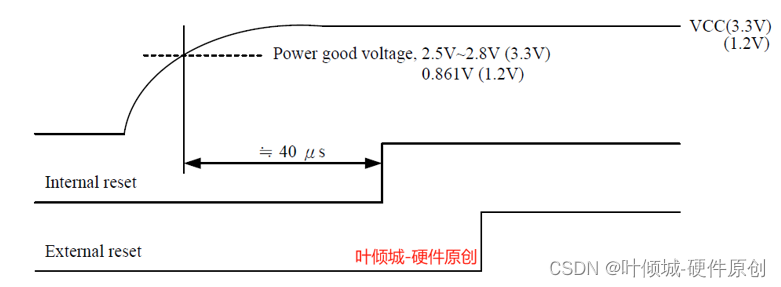

2.3.1、RESET Setting

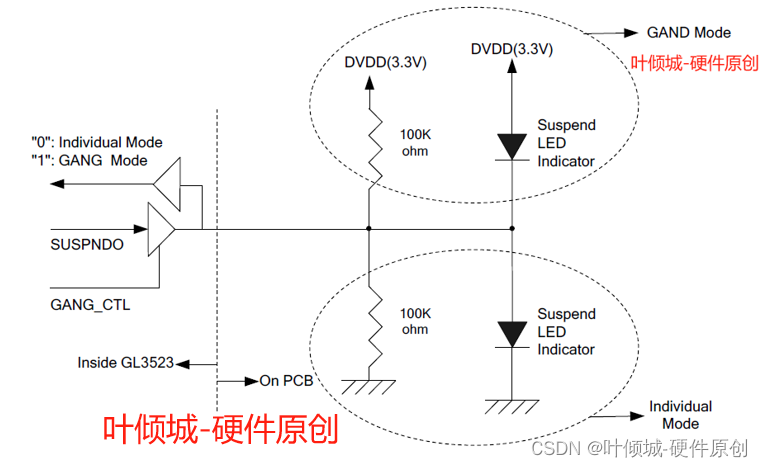

2.3.2、PGANG Setting

2.3.3、CHIPENABLE

2.3.4、PWREN1~4J

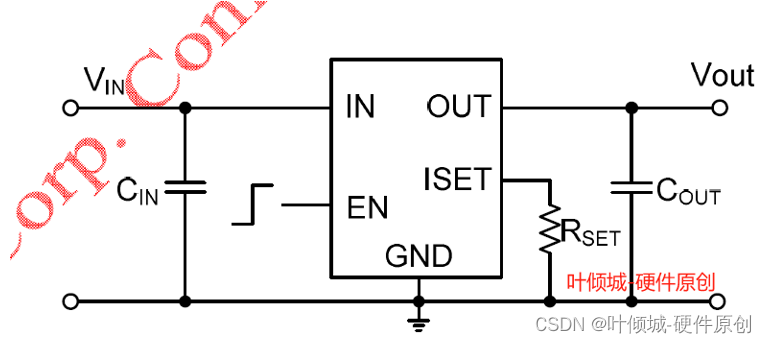

3、限流 Power Distribution Switch

3.1、矽力杰 SY6280

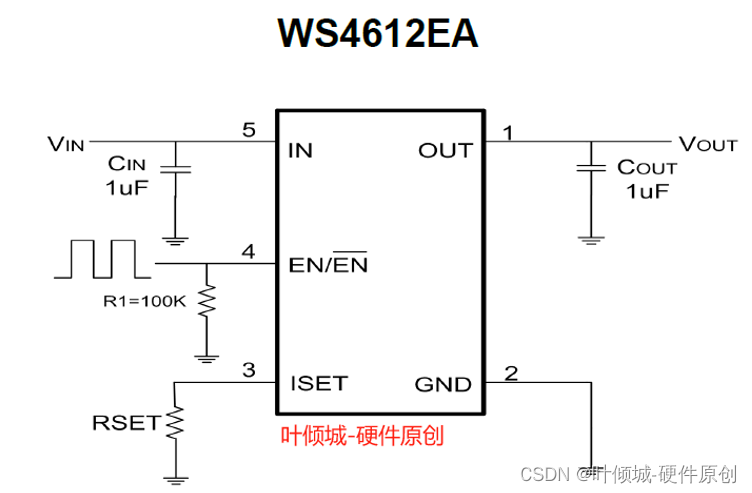

3.2、韦尔Will-WS4612E

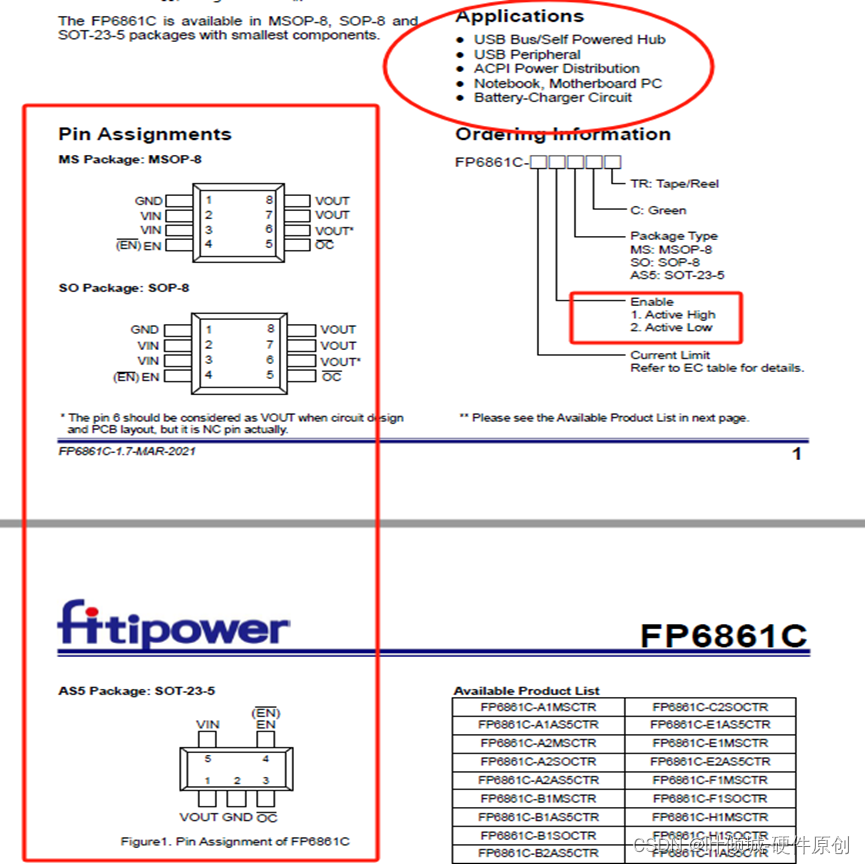

3.3、天钰-Fitipower FP6861C

4、硬件电路设计注意事项

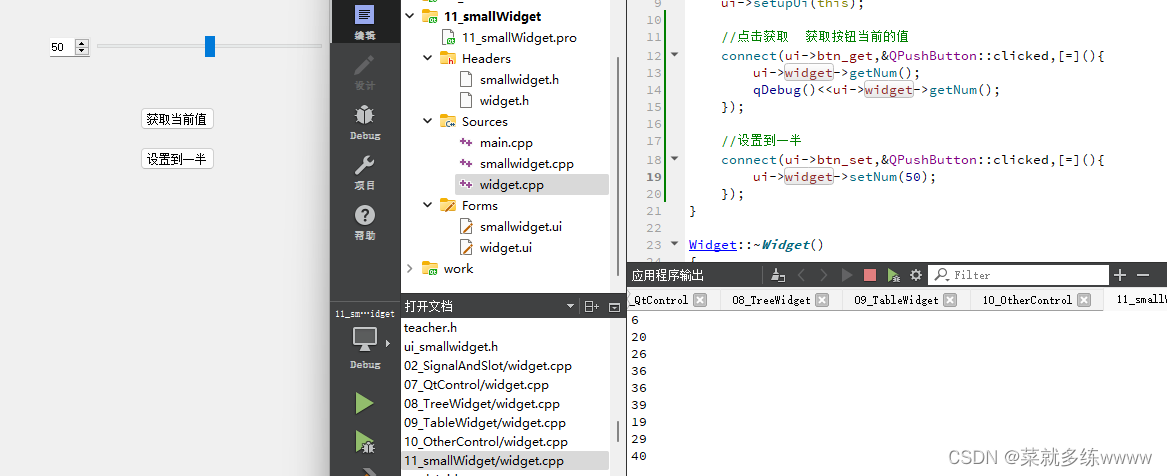

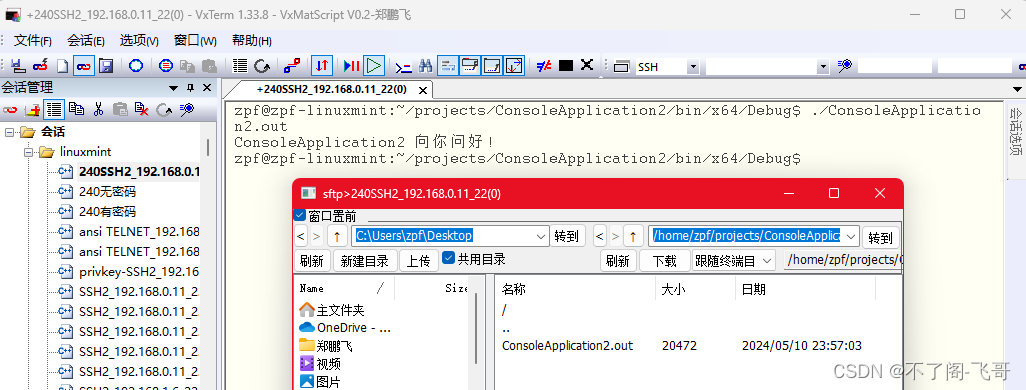

5、硬件实战

5.1、GL3523-S-QFN88硬件实战

5.2、GL3510-QFN64硬件实战

5.3、RTS5411硬件实战

6、USB layout设计要求

6.1、布局要求

1、USB接口靠近板边放置,避开其他高速信号

2、ESD保护器件和Common mode choke(共模电感、共模扼流圈)应该尽可能的靠近USB接口放置。

3、USB转换芯片与USB连接器应该尽可能的靠近,以减少走线的长度。其晶振不可放置过远,2个防漂移电容放晶振旁边。

4、用于去耦和消除高频噪声干扰的磁珠和去耦电容应该尽可能的靠近USB连接器放置。

5、USB电压稳压器尽可能靠近连接器放置。

6.2、布线要求

1、USB差分阻抗控制:USB2.0/USB3.0——90Ω(±10%),对内等长误差2mil。

2、USB差分信号尽量以完整的地平面为参考平面;

3、USB差分信号与其他时钟、高速信号保持至少5W以上间距。

4、USB电源线尽量粗,最好采用铺铜处理,USB2.0为0.5A,USB3.0为1A。并且机壳地与板内地的短接电感两端采用铺铜处理。