编写一个序列检测模块,检测输入信号a是否满足01110001序列,当信号满足该序列,给出指示信号match。

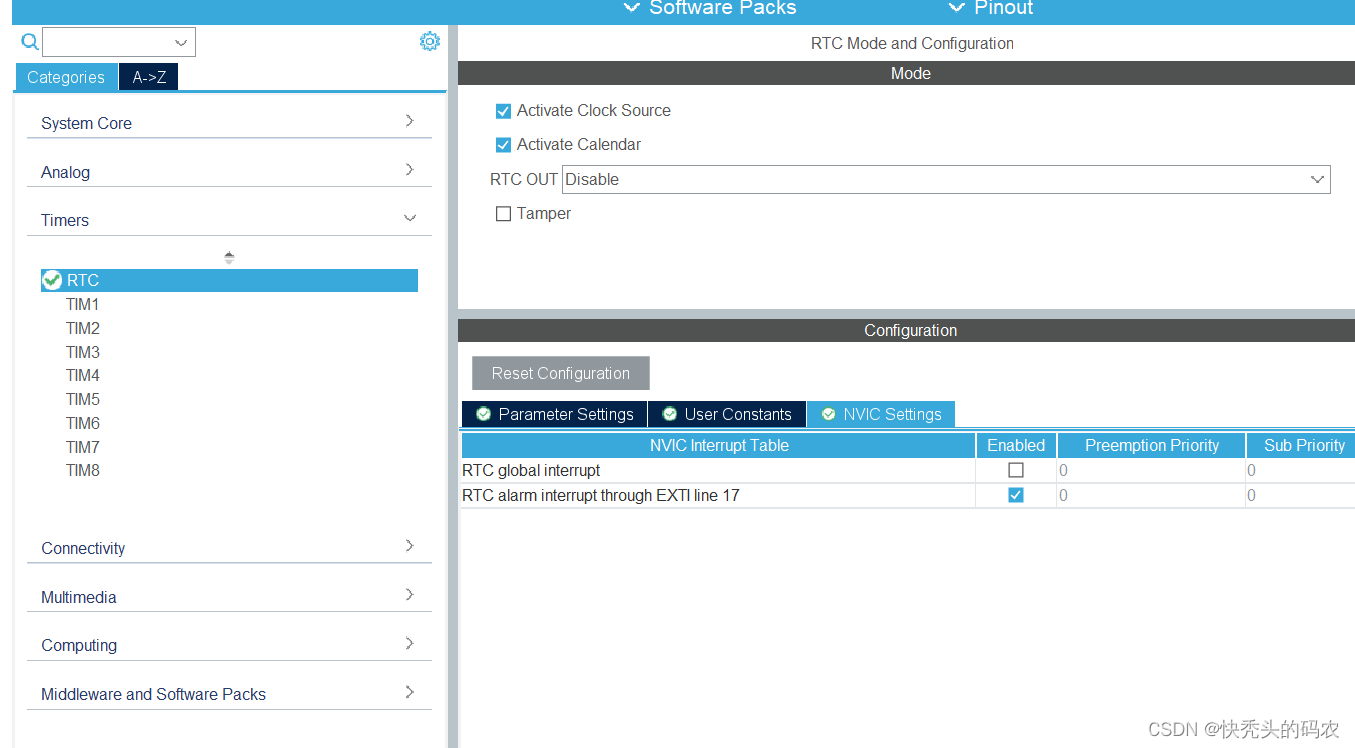

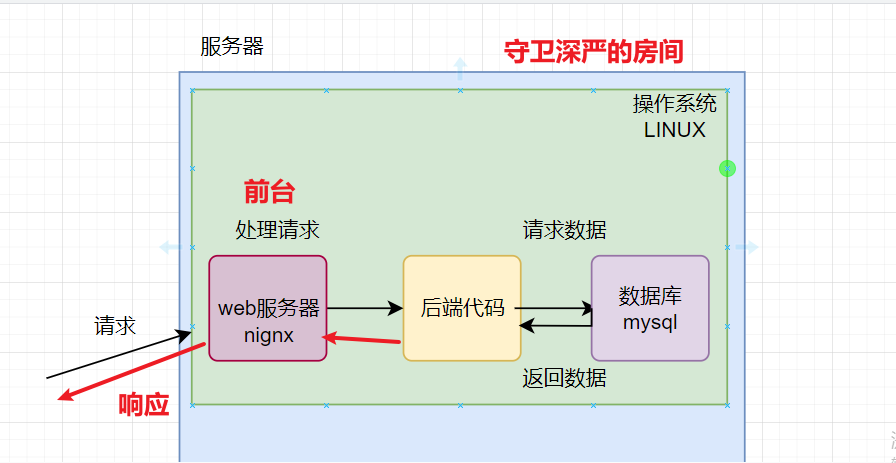

模块的接口信号图如下:

代码如下:

(CSDN代码块不支持Verilog,代码复制到notepad++编辑器中,语言选择Verilog,看得更清楚)

方法一:移位寄存器缓存

module sequence_detect(input clk,input rst_n,input a,output reg match

);reg[7:0] a_r;always@(posedge clk or negedge rst_n) beginif(~rst_n) begina_r<='b0;endelse begina_r<={a_r[6:0],a}; endendalways@(posedge clk or negedge rst_n) beginif(~rst_n) beginmatch <= 1'b0;endelse beginmatch <= a_r==8'b01110001;endend

endmodule

方法2:状态机写法

`timescale 1ns/1ns

module sequence_detect(input clk,input rst_n,input a,output reg match

);parameter ZERO=0, ONE=1, TWO=2, THREE=3, FOUR=4, FIVE=5, SIX=6, SEVEN=7, EIGHT=8;reg [3:0] state, nstate;always@(posedge clk or negedge rst_n) beginif(~rst_n)state <= ZERO;elsestate <= nstate;endalways@(*) begincase(state)ZERO : nstate = a? ZERO : ONE;ONE : nstate = a? TWO : ONE;TWO : nstate = a? THREE: ONE;THREE : nstate = a? FOUR : ONE;FOUR : nstate = a? ZERO : FIVE;FIVE : nstate = a? TWO : SIX;SIX : nstate = a? TWO : SEVEN;SEVEN : nstate = a? EIGHT: ONE;EIGHT : nstate = a? THREE: ONE ;default: nstate = ZERO;endcaseendalways@(posedge clk or negedge rst_n) beginif(~rst_n)match <= 0;elsematch <= state==EIGHT;endendmodule