Verilog语言支持

介绍

本章介绍AMD Vivado™对Verilog硬件描述的合成支持语言

本章包括编码示例。从“coding”下载编码示例文件示例。

Verilog设计

复杂电路的设计通常采用自上而下的方法。

•设计过程的每个阶段都需要不同的规范级别。例如,在体系结构级别,规范可以对应于框图或算法状态机(ASM)图表。

•块或ASM级对应于寄存器传输块,其中连接为N位线,例如:

○ 登记

○ 加法器

○ 柜台

○ 多路复用器

○ 互连逻辑

○ 有限状态机

•Verilog允许在计算机语言。

Verilog功能

Verilog提供行为语言结构和结构语言结构。这些结构允许设计对象在高抽象级别和低抽象级别的表达。

•使用Verilog设计硬件允许使用软件概念,例如:

○ 并行处理

○ 面向对象编程

•Verilog的语法类似于C和Pascal。

•Vivado综合支持Verilog作为IEEE 1364。

•Vivado合成中的Verilog支持允许您在中描述全局电路和每个块最有效的风格。

○ 以每个块的最佳合成流程进行合成。

○ 本文中的综合是高级行为和结构Verilog的编译

HDL语句转换为平坦的门级网表。网表可用于对诸如Virtex设备之类的可编程逻辑设备进行定制编程。

○ 不同的合成方法用于:

•算术块

•互连逻辑

•有限状态机(FSM)组件

有关Verilog基本概念的信息,请参阅IEEE Verilog HDL参考手册。

Verilog-2001支持

Vivado synthesis支持以下Verilog-2001功能。

•生成报表

•组合端口/数据类型声明

•ANSI样式的端口列表

•模块操作员端口列表

•ANSI C风格的任务/函数声明

•逗号分隔的灵敏度列表

•组合逻辑灵敏度

•具有连续分配的默认网络

•禁用默认网络声明

•索引矢量部分选择

•多维阵列

•网络和真实数据类型阵列

•阵列位和部件选择

•已签署的注册、网络和端口声明

•基于符号的整数

•有符号算术表达式

•算术移位运算符

•超过32位的自动宽度扩展

•电力操作员

•N大小的参数

•显式内联参数传递

•固定的本地参数

•增强的条件编译

•文件和行编译器指令

•可变部件选择

•递归任务和函数

•常数函数

有关更多信息,请参阅:

•斯图尔特•萨瑟兰。Verilog 2001:Verilog硬件描述的新功能指南语言(2002)

•IEEE标准Verilog硬件描述语言手册(IEEE标准1364-2001)

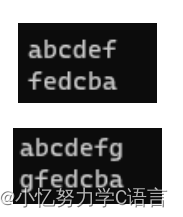

Verilog-2001可变零件选择

Verilog-2001允许您使用变量从矢量中选择一组位。

变量零件选择不是由两个显式值限定的,而是由其范围的点和矢量的宽度。零件选择的起点可能会有所不同。这个零件选择的宽度保持不变。

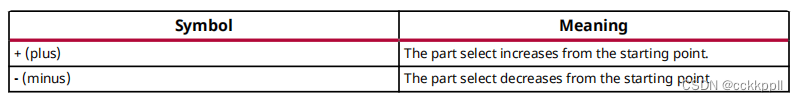

下表列出了可变零件选择符号。

结构Verilog

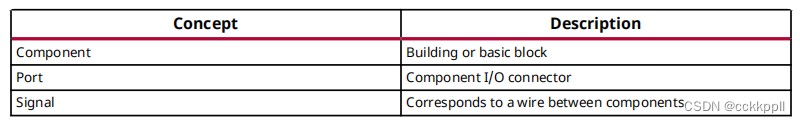

结构化Verilog描述汇集了几个代码块,并允许引入设计中的层次结构。下表列出了硬件结构的概念及其描述。

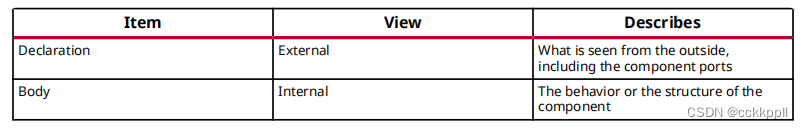

下表列出了Verilog组件、视图以及组件描述。

•组件由设计模块表示。

•组件之间的连接在组件实例化中指定声明。

•组件实例化语句:

○ 指定出现在另一个零部件或回路中的零部件实例

○ 用标识符标记。

○ 命名在本地组件声明中声明的组件。

○ 包含一个关联列表(带括号的列表)。该列表指定信号和端口与给定的本地端口相关联。

内置逻辑门

Verilog提供了一大组内置逻辑门,这些逻辑门被实例化以构建更大的逻辑电路。内置逻辑门所描述的一组逻辑功能包括:

•以及

•或

•XOR

•NAND

•NOR

•不是

2输入XOR函数示例

在这个编码示例中,内置模块的每个实例都有一个唯一的实例化名称如a_inv、b_inv和out。

实例化预定义的基本体

Verilog的结构特征允许您通过实例化预定义的电路来设计电路基元,例如:门、寄存器和AMD特定基元,如CLKDLL和BUFG。这些基元是Verilog中包含的基元的附加基元,并随AMD一起提供Verilog库(unisim_comp.v)。

实例化FDC和BUFG基元示例

unisim_comp.v库文件包括FDC和BUFG的定义。

![代码随想录算法训练营第三十二天 | 122.买卖股票的最佳时机 II,55. 跳跃游戏, 45.跳跃游戏 II[贪心算法篇]](https://img-blog.csdnimg.cn/direct/9545038056fb415f8560577fc80e05d7.png)

![gcd+线性dp,[蓝桥杯 2018 国 B] 矩阵求和](https://img-blog.csdnimg.cn/direct/089dfcfe8ad64cef994d8e798dcd2922.png)