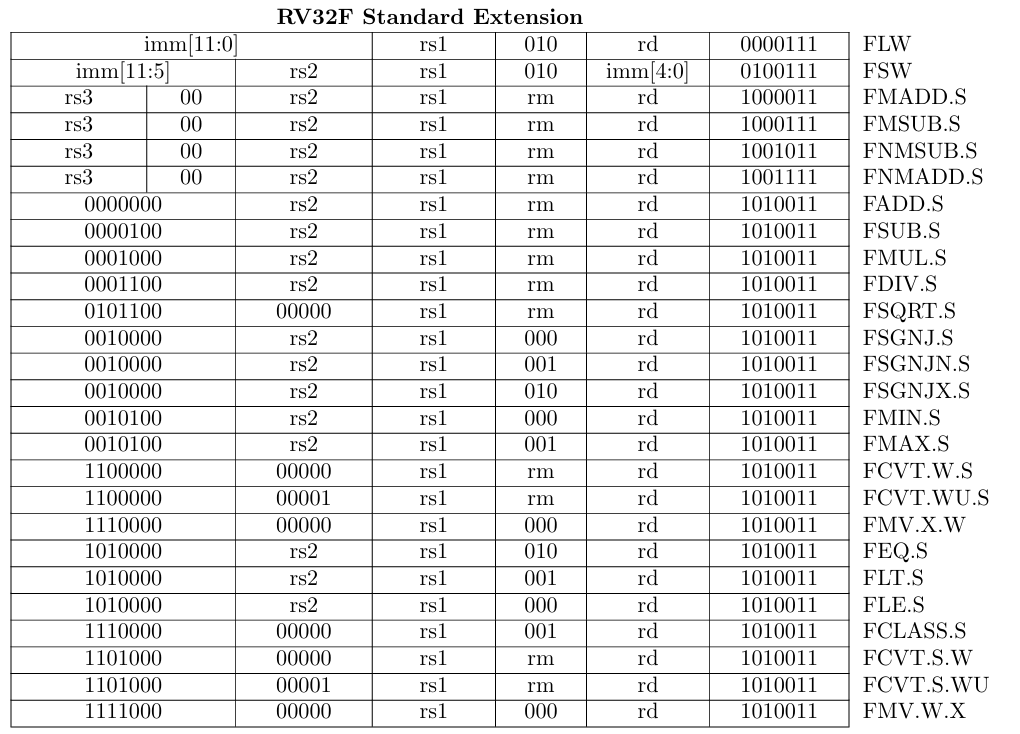

跟踪解码流程可以发现,解码主要是读取 instruction.cpp 里存储的指令集数组进行解码的。

那么对于实现 F 扩展指令集,第一步能成功读取识别新指令,就需要从这里入手。

解码部分代码:

static inline const struct InstructionMap &InstructionMapFind(uint32_t code) {const struct InstructionMap *im = &C_inst_map[instruction_map_opcode_field.decode(code)];while (im->subclass != nullptr) {im = &im->subclass[im->subfield.decode(code)];}if ((code ^ im->code) & im->mask) {return C_inst_unknown;}return *im;

}

具体解释:首先读取指令[1:0]位,并在 C_inst_map 数组中找到对应的指令集数组进行进一步解码。

static const struct InstructionMap C_inst_map[] = {IM_UNKNOWN,IM_UNKNOWN,IM_UNKNOWN,{"i", IT_UNKNOWN, NOALU, NOMEM, I_inst_map, {}, 0x3, 0x3, { .subfield = {5, 2} }, nullptr},

};

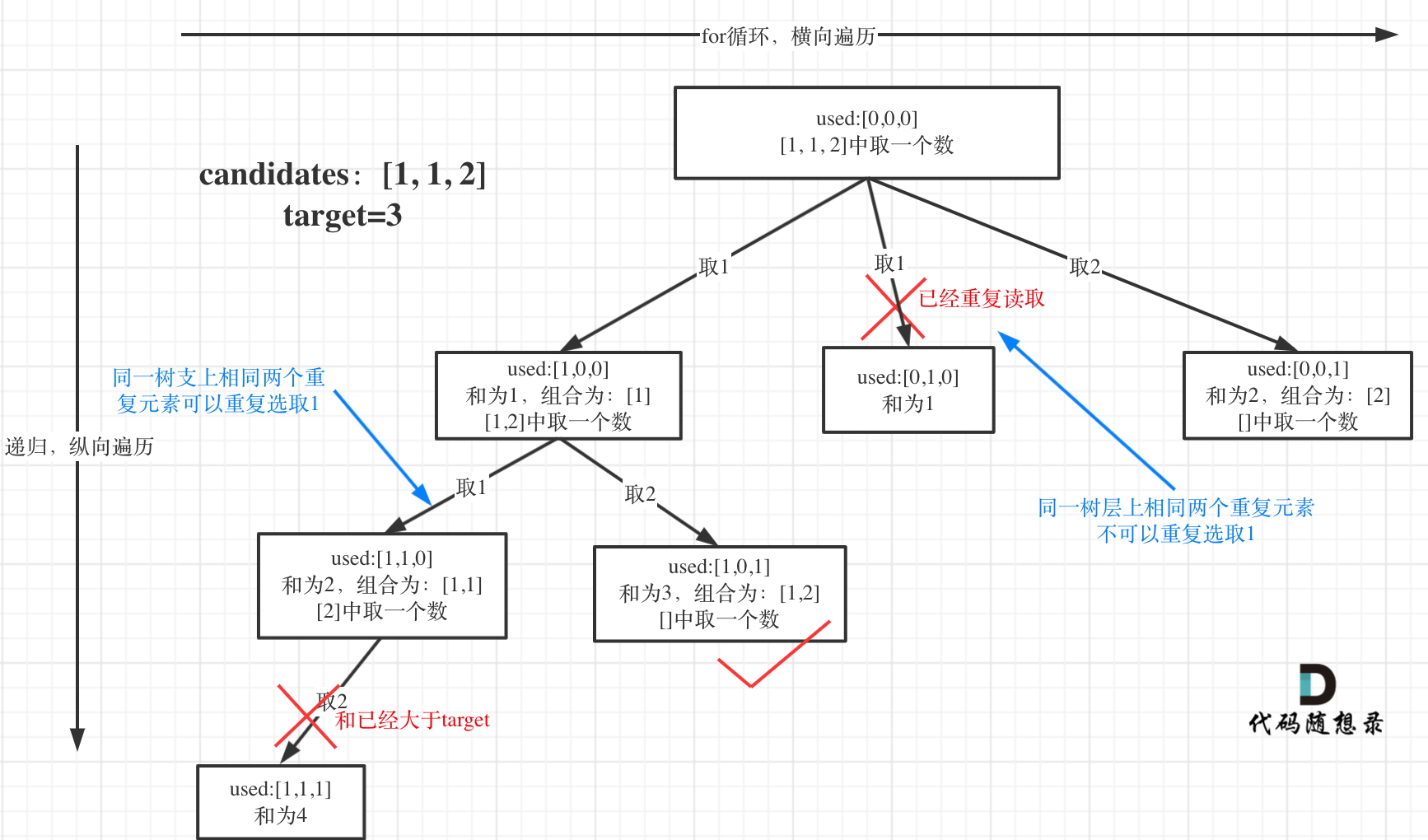

由于 i 指令和 F 指令最后两位都是11(也就是3,C_inst_map 指令集的第3项)因此按照这个指令解码方式两个指令集都应该存储到 I_inst_map 中。解码是参照指令的 [5:2] 位进行的,对于部分相同的指令(比如 lh lw 指令的 [5:2]位就一样)则全部存储到同一个 sub array 中进行进一步递归解码。

static const struct InstructionMap I_inst_map[] = {{"load", IT_I, NOALU, NOMEM, LOAD_map, {}, 0x03, 0x7f, { .subfield = {3, 12} }, nullptr}, // LOADIM_UNKNOWN, // LOAD-FPIM_UNKNOWN, // custom-0{"misc-mem", IT_I, NOALU, NOMEM, MISC_MEM_map, {}, 0x0f, 0x7f, { .subfield = {3, 12} }, nullptr}, // MISC-MEM{"op-imm", IT_I, NOALU, NOMEM, OP_IMM_map, {}, 0x13, 0x7f, { .subfield = {3, 12} }, nullptr}, // OP-IMM{"auipc", IT_U, { .alu_op=AluOp::ADD }, NOMEM, nullptr, {"d", "u"}, 0x17, 0x7f, { .flags = IMF_SUPPORTED | IMF_ALUSRC | IMF_REGWRITE | IMF_PC_TO_ALU }, nullptr}, // AUIPC{"op-imm-32", IT_I, NOALU, NOMEM, OP_IMM_32_map, {}, 0x1b, 0x7f, { .subfield = {3, 12} }, nullptr}, // OP-IMM-32 IM_UNKNOWN, // OP-IMM-32IM_UNKNOWN, // 48b{"store", IT_I, NOALU, NOMEM, STORE_map, {}, 0x23, 0x7f, { .subfield = {3, 12} }, nullptr}, // STOREIM_UNKNOWN, // STORE-FPIM_UNKNOWN, // custom-1{"amo", IT_R, NOALU, NOMEM, AMO_map, {}, 0x2f, 0x7f, { .subfield = {3, 12} }, nullptr}, // OP-32{"op", IT_R, NOALU, NOMEM, OP_map, {}, 0x33, 0x7f, { .subfield = {1, 25} }, nullptr}, // OP{"lui", IT_U, { .alu_op=AluOp::ADD }, NOMEM, nullptr, {"d", "u"}, 0x37, 0x7f, { .flags = IMF_SUPPORTED | IMF_ALUSRC | IMF_REGWRITE }, nullptr}, // LUI{"op-32", IT_R, NOALU, NOMEM, OP_32_map, {}, 0x3b, 0x7f, { .subfield = {1, 25} }, nullptr}, // OP-32IM_UNKNOWN, // 64bIM_UNKNOWN, // MADDIM_UNKNOWN, // MSUBIM_UNKNOWN, // NMSUBIM_UNKNOWN, // NMADDIM_UNKNOWN, // OP-FPIM_UNKNOWN, // reservedIM_UNKNOWN, // custom-2/rv128IM_UNKNOWN, // 48b{"branch", IT_B, NOALU, NOMEM, BRANCH_map, {}, 0x63, 0x7f, { .subfield = {3, 12} }, nullptr}, // BRANCH{"jalr", IT_I, { .alu_op=AluOp::ADD }, NOMEM, nullptr, {"d", "o(s)"}, 0x67, 0x7f, { .flags =

IMF_SUPPORTED | IMF_REGWRITE | IMF_BRANCH_JALR | IMF_ALUSRC | IMF_ALU_REQ_RS }, inst_aliases_jalr}, // JALRIM_UNKNOWN, // reserved{"jal", IT_J, { .alu_op=AluOp::ADD }, NOMEM, nullptr, {"d", "a"}, 0x6f, 0x7f, { .flags =

IMF_SUPPORTED |

IMF_REGWRITE | IMF_JUMP | IMF_PC_TO_ALU | IMF_ALUSRC }, inst_aliases_jal}, // JAL{"system", IT_I, NOALU, NOMEM, SYSTEM_map, {}, 0x73, 0x7f, { .subfield = {3, 12} }, nullptr}, // SYSTEMIM_UNKNOWN, // reservedIM_UNKNOWN, // custom-3/rv128IM_UNKNOWN, // >= 80b

};

那么参照 F 指令集,我在 I_inst_map 基础上继续添加新的指令:

对于 opcode 唯一的指令直接在 I_inst_map 中实现即可,对于 opcode 重复的指令则在 F_inst_map 中根据 [31:25] 位进一步解码。这里我暂时只写了 add 和 sub。

static const struct InstructionMap F_inst_map[] = {{"fadd.s",IT_I, NOALU, NOMEM, nullptr, {}, 0x53, 0x7f, {}, nullptr},{"fsub.s",IT_I, NOALU, NOMEM, nullptr, {}, 0x53, 0x7f, {}, nullptr},

};static const struct InstructionMap I_inst_map[] = {{"load", IT_I, NOALU, NOMEM, LOAD_map, {}, 0x03, 0x7f, { .subfield = {3, 12} }, nullptr}, // LOAD{"load-fp", IT_I, NOALU, NOMEM, nullptr, {}, 0x03, 0x7f, {}, nullptr}, // LOAD-FPIM_UNKNOWN, // custom-0{"misc-mem", IT_I, NOALU, NOMEM, MISC_MEM_map, {}, 0x0f, 0x7f, { .subfield = {3, 12} }, nullptr}, // MISC-MEM{"op-imm", IT_I, NOALU, NOMEM, OP_IMM_map, {}, 0x13, 0x7f, { .subfield = {3, 12} }, nullptr}, // OP-IMM{"auipc", IT_U, { .alu_op=AluOp::ADD }, NOMEM, nullptr, {"d", "u"}, 0x17, 0x7f, { .flags = IMF_SUPPORTED | IMF_ALUSRC | IMF_REGWRITE | IMF_PC_TO_ALU }, nullptr}, // AUIPC{"op-imm-32", IT_I, NOALU, NOMEM, OP_IMM_32_map, {}, 0x1b, 0x7f, { .subfield = {3, 12} }, nullptr}, // OP-IMM-32 IM_UNKNOWN, // OP-IMM-32IM_UNKNOWN, // 48b{"store", IT_I, NOALU, NOMEM, STORE_map, {}, 0x23, 0x7f, { .subfield = {3, 12} }, nullptr}, // STORE{"store-fp", IT_I, NOALU, NOMEM, nullptr, {}, 0x03, 0x7f, {}, nullptr}, // STORE-FPIM_UNKNOWN, // custom-1{"amo", IT_R, NOALU, NOMEM, AMO_map, {}, 0x2f, 0x7f, { .subfield = {3, 12} }, nullptr}, // OP-32{"op", IT_R, NOALU, NOMEM, OP_map, {}, 0x33, 0x7f, { .subfield = {1, 25} }, nullptr}, // OP{"lui", IT_U, { .alu_op=AluOp::ADD }, NOMEM, nullptr, {"d", "u"}, 0x37, 0x7f, { .flags = IMF_SUPPORTED | IMF_ALUSRC | IMF_REGWRITE }, nullptr}, // LUI{"op-32", IT_R, NOALU, NOMEM, OP_32_map, {}, 0x3b, 0x7f, { .subfield = {1, 25} }, nullptr}, // OP-32IM_UNKNOWN, // 64b{"fmadd.s", IT_I, NOALU, NOMEM, nullptr, {}, 0x43, 0x7f, {}, nullptr}, // FMADD.S{"fmsub.s", IT_I, NOALU, NOMEM, nullptr, {}, 0x47, 0x7f, {}, nullptr}, // FMSUB.S{"fnmsub.s", IT_I, NOALU, NOMEM, nullptr, {}, 0x4b, 0x7f, {}, nullptr}, // FNMSUB.S{"fnmadd.s", IT_I, NOALU, NOMEM, nullptr, {}, 0x4f, 0x7f, {}, nullptr}, // FNMADD.S{"op-fp",IT_I, NOALU, NOMEM, F_inst_map, {}, 0x53, 0x7f, {}, nullptr}, // OP-FPIM_UNKNOWN, // reservedIM_UNKNOWN, // custom-2/rv128IM_UNKNOWN, // 48b{"branch", IT_B, NOALU, NOMEM, BRANCH_map, {}, 0x63, 0x7f, { .subfield = {3, 12} }, nullptr}, // BRANCH{"jalr", IT_I, { .alu_op=AluOp::ADD }, NOMEM, nullptr, {"d", "o(s)"}, 0x67, 0x7f, { .flags =

IMF_SUPPORTED | IMF_REGWRITE | IMF_BRANCH_JALR | IMF_ALUSRC | IMF_ALU_REQ_RS }, inst_aliases_jalr}, // JALRIM_UNKNOWN, // reserved{"jal", IT_J, { .alu_op=AluOp::ADD }, NOMEM, nullptr, {"d", "a"}, 0x6f, 0x7f, { .flags =

IMF_SUPPORTED |

IMF_REGWRITE | IMF_JUMP | IMF_PC_TO_ALU | IMF_ALUSRC }, inst_aliases_jal}, // JAL{"system", IT_I, NOALU, NOMEM, SYSTEM_map, {}, 0x73, 0x7f, { .subfield = {3, 12} }, nullptr}, // SYSTEMIM_UNKNOWN, // reservedIM_UNKNOWN, // custom-3/rv128IM_UNKNOWN, // >= 80b

};下一步 execute 阶段。